Voor de vierde achtereenvolgende dag verpletterden we de concurrentie met een flush van meer dan 4M. ![]()

Ons ledenaantal groeide met 6 leden tot 4654. Wil jij ook meedoen? Kijk dan hier hoe je ook jouw pc's van een koetje kunt voorzien.

Er zijn nog steeds mensen die client 8012 gebruiken, denk eraan dat jullie blocks straks geweigerd gaan worden. Zie voor meer informatie deze thread op GoT.

DPC top 30 van 1 maart

| 1. | ( 1609) 1609) | 486.547 | - Team Frikandel Speciaal | 3.124.453 | (37) |

| 2. | ( 1) 1) | 217.194 | Division Eindhoven | 2.831.208 | (42) |

| 3. | ( 1635) 1635) | 143.010 | The Lightning Crew | 450.841 | (299) |

| 4. | ( 3) 3) | 128.952 | AUGUSTIJN | 3.479.741 | (34) |

| 5. | ( 1222) 1222) | 105.282 | De beste koei'n bint twentse koei'n | 290.029 | (435) |

| 6. | ( 2) 2) | 100.602 | Ethan_Hunt | 13.196.449 | (6) |

| 7. | ( 1) 1) | 79.054 | Quakers United | Cewle Coown' Cadavers | 17.184.437 | (4) |

| 8. | ( 2) 2) | 72.372 | Bill Goldberg | 19.229.064 | (3) |

| 9. | ( 2) 2) | 66.009 | DBC | 16.974.522 | (5) |

| 10. | ( 3) 3) | 64.873 | -Killemall says: may the cow be with you | 11.035.685 | (7) |

| 11. | ( 40) 40) | 58.085 | Schumi | 1.901.247 | (66) |

| 12. | ( ) ) | 56.421 | wiho | 20.594.307 | (1) |

| 13. | ( 3) 3) | 51.642 | Team Casema slachtoffers | 652.127 | (222) |

| 14. | ( 5) 5) | 48.315 | TexelCows | 873.089 | (168) |

| 15. | ( 13) 13) | 44.857 | I 'R Cow @ I-netcafe Groningen | 4.841.883 | (19) |

| 16. | ( 13) 13) | 43.520 | De Utregse Kudde | 1.004.420 | (131) |

| 17. | ( 12) 12) | 43.483 | Clan-of-nine | 7.646.774 | (9) |

| 18. | ( 8) 8) | 42.010 | Team BVD | 3.818.275 | (28) |

| 19. | ( 36) 36) | 41.063 | Koetje.org | 2.667.269 | (45) |

| 20. | ( 1118) 1118) | 34.549 | Mad Cow Clan | 288.300 | (439) |

| 21. | ( 288) 288) | 34.224 | STeaLTH, Marius | 811.116 | (177) |

| 22. | ( 8) 8) | 33.887 | [Groningen] Noorder Power Cows | 3.617.680 | (30) |

| 23. | ( 2) 2) | 32.063 | Ronnie Tober NO Devote! | 2.117.976 | (58) |

| 24. | ( 249) 249) | 32.021 | [DutchPowerCows]AnthillMOBB | 386.073 | (338) |

| 25. | ( ) ) | 31.387 | United DivX'ers | 181.204 | (632) |

| 26. | ( 12) 12) | 29.609 | Team BoGoH | 3.786.435 | (29) |

| 27. | ( 7) 7) | 28.774 | Rulende_Bikkels & Panic IRC | 5.949.524 | (12) |

| 28. | ( 695) 695) | 27.786 | KNKB L@N Flush - greetz Zeb! | 518.509 | (267) |

| 29. | ( 3) 3) | 27.720 | Interior Lulu | 19.634.281 | (2) |

| 30. | ( 6) 6) | 24.305 | Team |>Just dU It!<| | 4.984.015 | (17) |

De 15 grootste stijgers

| Pixilated NetphreaX |  1647 1647 | (59.) | 13.147 |

| The Lightning Crew |  1635 1635 | (3.) | 143.010 |

| - Team Frikandel Speciaal |  1609 1609 | (1.) | 486.547 |

| Mac |  1566 1566 | (80.) | 8.185 |

| Smallie |  1518 1518 | (84.) | 7.726 |

| Robocom |  1312 1312 | (146.) | 3.913 |

| Clan-of-Nine backup :-) |  1287 1287 | (214.) | 2.464 |

| PoerQwa |  1248 1248 | (461.) | 998 |

| -=DPC=- [NCGQ]Mr.Fox |  1248 1248 | (254.) | 2.088 |

| De beste koei'n bint twentse koei'n |  1222 1222 | (5.) | 105.282 |

| PongFlushers |  1208 1208 | (160.) | 3.476 |

| Mad Cow Clan |  1118 1118 | (20.) | 34.549 |

| Stoffel de Schildpad |  1097 1097 | (110.) | 5.313 |

| PvK |  1079 1079 | (354.) | 1.426 |

| Cow and Chicken ( DPC ) |  1072 1072 | (323.) | 1.551 |

Top 15 teams

| 1. | ( ) ) | 4.298.244 | Dutch Power Cows | 739.552.450 | (1) |

| 2. | ( ) ) | 1.772.674 | AnandTech | 682.961.379 | (2) |

| 3. | ( ) ) | 1.271.194 | HackZone Team -- Combined power of Russia and exUSSR countries | 458.320.637 | (4) |

| 4. | ( ) ) | 1.174.671 | Russian Team | 456.423.455 | (5) |

| 5. | ( ) ) | 676.591 | Slashdot.org | 578.358.322 | (3) |

| 6. | ( ) ) | 651.632 | Ars Technica Team Beef Roast | 120.735.475 | (23) |

| 7. | ( 2) 2) | 545.275 | Team EvangeLista (Macs Rule! :-) | 416.321.021 | (6) |

| 8. | ( ) ) | 536.764 | Japan Linux Users Group | 239.391.733 | (10) |

| 9. | ( 2) 2) | 507.064 | The Amiga RC5 Team effort | 319.198.926 | (8) |

| 10. | ( ) ) | 421.592 | Japan FreeBSD Users Group | 249.718.453 | (9) |

| 11. | ( ) ) | 404.354 | Japan Windows NT Users Group | 224.902.528 | (11) |

| 12. | ( ) ) | 387.665 | Team Warped (OS/2) | 321.378.199 | (7) |

| 13. | ( ) ) | 319.077 | Ukraine RC5 | 106.273.711 | (26) |

| 14. | ( ) ) | 317.598 | Team Depaul | 59.148.488 | (47) |

| 15. | ( ) ) | 306.036 | SysOpt.com/Tweakit.com | 136.940.307 | (20) |

Mijlpalen

| -Killemall says: may the cow be with you | 11.000.000 |

| Total Grazing Addicts | 5.000.000 |

| - Team Frikandel Speciaal | 3.000.000 |

| De Utregse Kudde | 1.000.000 |

| STeaLTH, Marius | 800.000 |

| Stoffel de Schildpad | 700.000 |

| KNKB L@N Flush - greetz Zeb! | 500.000 |

| Mac | 400.000 |

| www gameoverlan.com LANNEUH! | 400.000 |

| The Lightning Crew | 400.000 |

| Bastards | 400.000 |

| Joost Klootwijk | 300.000 |

| De beste koei'n bint twentse koei'n | 200.000 |

| AxeWeb.nl & Sector17.nu | 200.000 |

| Huizer Jojo koeien | 100.000 |

| Black.Adder | 100.000 |

| Rotterdamsche Runderen Societeit | 100.000 |

Leden

| Aantal leden | 4654 |

| Verschil met vorige dag | 3 |

| Nieuwe leden | 6 |

| Retirements | 0 |

Welkom bij DPC GeoGis, Tubbiepo, jdeboer.aut, memmaker, arjan_driel en Floris Dansen!

Revenue in February rose to NT$3.3 billion ($102 million). Via said its chipsets, which connect all the

components of a computer's motherboard, accounted for more than four-fifths of February sales.

Revenue in February rose to NT$3.3 billion ($102 million). Via said its chipsets, which connect all the

components of a computer's motherboard, accounted for more than four-fifths of February sales.

Prototype Serial ATA PCs were on show, demonstrating hot

pluggable hard disks. But only for Linux users. The Windows drivers

doesn't have the functionality at the moment. Right now the Linux

demo makes the physical connection, creates a mount point, mounts

the file system, and drops a new icon onto the desktop transparently.

You still have to press a release button on the drive to undock the

unit, although we're sure someone will find a way to do this by

dragging it to the wastebasket.

Prototype Serial ATA PCs were on show, demonstrating hot

pluggable hard disks. But only for Linux users. The Windows drivers

doesn't have the functionality at the moment. Right now the Linux

demo makes the physical connection, creates a mount point, mounts

the file system, and drops a new icon onto the desktop transparently.

You still have to press a release button on the drive to undock the

unit, although we're sure someone will find a way to do this by

dragging it to the wastebasket. LT: It's very much been a part of the motivational thing to always have something to compare against. If you don't have anything to compare against, it's very hard to make good judgments on what you're good at and what you're bad at. For example, one of the issues last year was the MindCraft thing [MindCraft is an independent research laboratory that last year reported test results -- paid for by Microsoft -- indicating that Windows NT outperformed Linux in certain basic server tasks. Ed].

LT: It's very much been a part of the motivational thing to always have something to compare against. If you don't have anything to compare against, it's very hard to make good judgments on what you're good at and what you're bad at. For example, one of the issues last year was the MindCraft thing [MindCraft is an independent research laboratory that last year reported test results -- paid for by Microsoft -- indicating that Windows NT outperformed Linux in certain basic server tasks. Ed].

De kans dat je een pc aanzet en iets anders dan een Windows-besturingssysteem ziet verschijnen is ongeveer een op tien. Zelfs na de moeizame introductie van Windows 2000 en de groeiende populariteit van alternatieve besturingssystemen, blijven de Microsoft OS-en 92 procent van de markt bezitten. De cijfers staan te lezen in het 'Client Operating Environments: 2000 Year in Review'-rapport van onderzoeksbureau IDC.

De kans dat je een pc aanzet en iets anders dan een Windows-besturingssysteem ziet verschijnen is ongeveer een op tien. Zelfs na de moeizame introductie van Windows 2000 en de groeiende populariteit van alternatieve besturingssystemen, blijven de Microsoft OS-en 92 procent van de markt bezitten. De cijfers staan te lezen in het 'Client Operating Environments: 2000 Year in Review'-rapport van onderzoeksbureau IDC.

A computerised toddler called Hal is the first artificial intelligence program to "understand" everyday language, say its creators.

A computerised toddler called Hal is the first artificial intelligence program to "understand" everyday language, say its creators.

The revised revenue estimate is largely a result of weaker personal

computer sales worldwide, ATI said. [...] The company cited lower revenue and a one-time higher

cost for memory as the primary reasons for the shortfall in earnings.

The revised revenue estimate is largely a result of weaker personal

computer sales worldwide, ATI said. [...] The company cited lower revenue and a one-time higher

cost for memory as the primary reasons for the shortfall in earnings.

Santa Clara, Calif. - February 27, 2001 - Broadcom's (Nasdaq: BRCM) ServerWorks subsidiary, the leading

independent supplier of high-performance SystemI/O™ integrated circuits for servers, today unveiled details of

its Grand Champion™ HE architecture for Intelâ-based multiprocessor platforms. ServerWorks' Grand

Champion HE architecture delivers an unprecedented 6.4 Gigabytes per second of memory bandwidth and up

to 5 GBytes/second of I/O throughput, supporting a maximum of six independent PCI-X bus segments and one

traditional 32-bit PCI bus.

Santa Clara, Calif. - February 27, 2001 - Broadcom's (Nasdaq: BRCM) ServerWorks subsidiary, the leading

independent supplier of high-performance SystemI/O™ integrated circuits for servers, today unveiled details of

its Grand Champion™ HE architecture for Intelâ-based multiprocessor platforms. ServerWorks' Grand

Champion HE architecture delivers an unprecedented 6.4 Gigabytes per second of memory bandwidth and up

to 5 GBytes/second of I/O throughput, supporting a maximum of six independent PCI-X bus segments and one

traditional 32-bit PCI bus.

"The corporate IT Nazis are absolute fanatics about having a solid, reliable platform," McCarron

said. "The experience with the 820 chipset (Intel's Rambus chipset in 1999) put a lot of them

off on pushing Rambus in the corporate market."

This "certainly helps" AMD, he added.

"The corporate IT Nazis are absolute fanatics about having a solid, reliable platform," McCarron

said. "The experience with the 820 chipset (Intel's Rambus chipset in 1999) put a lot of them

off on pushing Rambus in the corporate market."

This "certainly helps" AMD, he added.

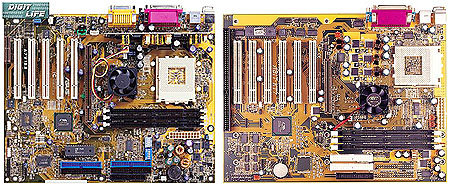

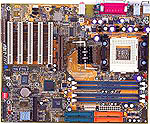

Het bord is genaamd TH7-RAID en is gebaseerd op de i850 chipset. Naast 4 RIMM slots heeft het plankje 5xPCI, 1xCNR en AGP4x. De toevoeging 'RAID' duidt zoals gewoonlijk op de aanwezigheid van een HighPoint HPT370 IDE RAID controller. Verder is er een 10/100Mbit Intel 82559 ethernet controller op het bord geïntegreerd. Vooralsnog is er op de

Het bord is genaamd TH7-RAID en is gebaseerd op de i850 chipset. Naast 4 RIMM slots heeft het plankje 5xPCI, 1xCNR en AGP4x. De toevoeging 'RAID' duidt zoals gewoonlijk op de aanwezigheid van een HighPoint HPT370 IDE RAID controller. Verder is er een 10/100Mbit Intel 82559 ethernet controller op het bord geïntegreerd. Vooralsnog is er op de