AMD heeft samen met Microsoft een conferentie gehouden in Japan, getiteld AMD & Microsoft Software Developer Conference. Hoewel deze conferentie zich vooral richtte op het ontwikkelen van software voor het Windows 64-bits Extended besturingssysteem, liet AMD ook zien wat er in de toekomst van het bedrijf te verwachten is. Ook lieten HP en IBM hun toekomstplannen met het AMD64-platform zien. Microsoft liet weten dat Windows XP 64-Bit Edition en Windows Server 2003 64-Bit Edition zowel AMD64 als de IA-32e-processors zullen ondersteunen. Een Japanse intermediaire beta-versie zal in juni verschijnen. Een Japanse pre-release beta is voor augustus gepland. De verkoop van beide besturingssystemen zal in het laatste kwartaal van dit jaar van start gaan.

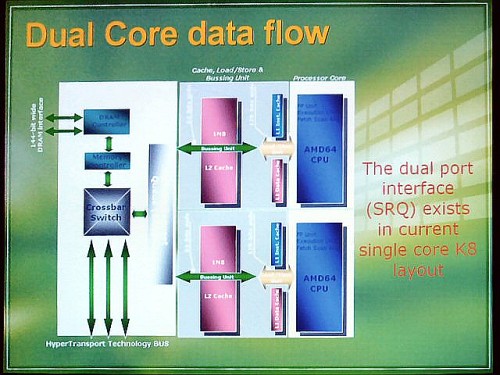

AMD laat weten dat het aftellen voor het 90nm-proces is begonnen. Op een van de getoonde dia's die het presenteerde is dan ook goed te zien dat 2004 het jaar van het 90nm-proces is. De geruchten dat het proces pas in 2005 zou worden gebruikt lijken hiermee dan ook ontkracht. Op diezelfde slide is ook te zien dat AMD van plan is om het 65nm-proces al in 2005 te gaan gebruiken. Waarschijnlijk is dit wel aan het eind van 2005, want eerdere berichten spraken nog over ergens in 2006. AMD bevestig nog maar eens met enkele slides de komst van een dual core-processor. Uit een van deze dia's blijkt dat de dual core-processor uitgerust zal zijn met twee identieke cpu's. Beiden hebben hun eigen L1 en L2-cache geheugen en kunnen via een interne bus met elkaar communiceren. Via deze bus zijn ze ook verbonden met een crossbar-switch waarop de geheugencontroller en de verschillende HyperTransport-bussen zijn aangesloten.