Op Ars Technica is een verhaal verschenen over drie processors waar op het Microprocessor Forum van vorige maand veel informatie naar buiten is gebracht, te weten: IBM Power5, Sun UltraSparc IV en Transmeta Efficeon. Naast het bespreken van de technische aspecten wil de schrijver ook een bepaalde rode draad blootleggen over de industrie in het algemeen.

![]() IBM Power5

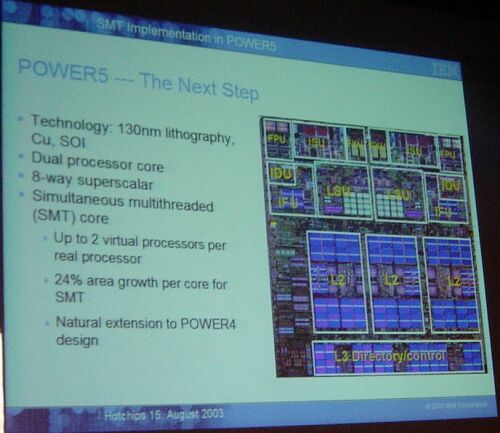

IBM Power5

De meest interessante nieuwe onthulling de op het MPF werd gedaan over de Power5 is dat deze chip een geavanceerde implementatie van SMT bevat, waarmee ten koste van 24% meer transistors significant betere prestaties behaald zouden worden. Anders dan bij x86 is de Power-architectuur gebaseerd op groepen van vijf instructies, en Power5 wordt de eerste generatie die twee van deze bundels tegelijk uit zijn L1-cache kan trekken. Door interne beperkingen kunnen er alsnog maar vijf operaties tegelijk uitgevoerd worden, maar omdat de processor nu dubbel zoveel opdrachten achter de hand heeft om zijn rekeneenheden mee bezig te houden, kunnen de prestaties met wel 40% toenemen. Een andere reden waarom er meer verwacht wordt van deze vorm van SMT dan van Intel's HyperThreading, is het feit dat IBM operating systemen de mogelijkheid geeft om invloed uit te oefenen op de werking van de feature, door threads prioriteiten toe te wijzen of zelfs het multithreading tijdelijk uit te schakelen, zodat alle rekenkracht voor één thread beschikbaar is.

![]() Sun UltraSparc IV

Sun UltraSparc IV

Sun pakt het iets minder subtiel aan plakt gewoon twee UltraSparc III-cores naast elkaar in een chip die op het bestaande socket past. Hoewel processors met meerdere cores al geruime tijd geleverd worden door IBM en HP, en deze zet dus vanuit het standpunt van de chipontwerper een stuk minder vernuftig of vernieuwend is, wil dat niet zeggen dat de aanpak niet werkt. Vooral omdat Sun zowel de hardware als het OS en de applicaties levert, heeft het bedrijf de mogelijkheid om maximaal te optimaliseren voor de gekozen route.

![]() Transmeta Efficeon

Transmeta Efficeon

Transmeta heeft met Efficieon het basisconcept van de Crusoë verder uitgewerkt. De chip is qua architectuur simpel gehouden door zo veel complexiteit naar de code-morphing software te verplaatsen. Hoewel het idee op zich leuk is en het ook gelukt is om een product neer te zetten dat in ieder geval op sommige gebieden kan concurreren met Intel Centrino, worden er grote vraagtekens gezet bij de toekomst van deze aanpak. De code-morphing software zelf gebruikt immers ook de nodige rekenkracht. Hoe meer optimalisaties nodig zijn, hoe meer de processor zichzelf bezig moet houden met een bijtaak waar andere chips gewoon aparte circuits voor hebben. Zeker omdat de snelheid en zuinigheid van een chip tegenwoordig meer afhankelijk zijn van de productietechnologie dan van de architectuur, vraagt de schrijver zich af of het wel de moeite waard is om het wiel opnieuw uit te vinden.

Transmeta heeft met Efficieon het basisconcept van de Crusoë verder uitgewerkt. De chip is qua architectuur simpel gehouden door zo veel complexiteit naar de code-morphing software te verplaatsen. Hoewel het idee op zich leuk is en het ook gelukt is om een product neer te zetten dat in ieder geval op sommige gebieden kan concurreren met Intel Centrino, worden er grote vraagtekens gezet bij de toekomst van deze aanpak. De code-morphing software zelf gebruikt immers ook de nodige rekenkracht. Hoe meer optimalisaties nodig zijn, hoe meer de processor zichzelf bezig moet houden met een bijtaak waar andere chips gewoon aparte circuits voor hebben. Zeker omdat de snelheid en zuinigheid van een chip tegenwoordig meer afhankelijk zijn van de productietechnologie dan van de architectuur, vraagt de schrijver zich af of het wel de moeite waard is om het wiel opnieuw uit te vinden.

De overeenkomst tussen deze drie chips is dat ze hun rekenkracht ieder op hun eigen manier zo goed mogelijk proberen gebruiken. Van de drie stappen die iedere chip volgt (data ophalen, iets ermee doen, data wegschrijven), is het gedeelte dat "iets doet" al vele jaren het makkelijkste om te bouwen. Het wegschrijven is weliswaar relatief traag, maar omdat daar meestal niet op gewacht hoeft te worden is dat niet zo'n probleem voor de performance. De latency bij het ophalen van data is dat echter wel, en een groeiend ook. De creatieve oplossingen die bedacht worden om ervoor te zorgen dat de processor toch genoeg werk heeft, zullen steeds meer tekenend zijn voor toekomstige generaties hardware en software:

I think that all three of the architectures I mentioned above illustrate in one way or another the ways in which increasing load latencies affect the entire hardware-software ecosystem, from the motherboard and CPU all the way up to the OS and end-user applications. I suppose that on some level, this is perhaps an obvious and almost trivial observation, but it's still remarkable to me just how these effects are working themselves out. And this is happening at all levels of system design as more and more devices get more and more connected while feature sizes continue to shrink. Latency matters at the level of the network, at the level of microprocessor layout due to wire delay, and at every level in between.