Transmeta heeft 14 oktober de Efficeon TM8600 en TM8620-processor officieel geïntroduceerd en de officiële specificaties bekendgemaakt, na al eerder de aankondigingen de wereld ingestuurd te hebben. Zoals al eerder bekend was, kan deze processor acht instructies per klokcyclus verwerken en is de architectuur gebaseerd op 256-bit oftewel het is een Very Long Instruction Word-processor. Daarnaast gaat de processor ook alle extra multimedia-instructies ondersteunen, zoals MMX, SSE en SSE2 en is er de beschikking over een 1MB L2-cache.

Naast deze ondersteuning heeft het bedrijf ook eigen software ontwikkeld om de processor beter te laten presteren: de tweede generatie van Code Morphing Software. Deze software draagt bij aan een efficiënter energiegebruik en een verbeterde reactiesnelheid met betrekking tot het verwerken van de verschillende instructies. Dit kunnen zowel RISC zijn als x86-instructies zijn. Dit alles laat de Efficeon een maximale kloksnelheid van 1,1GHz bereiken, terwijl er slechts zeven Watt aan energie zal worden gebruikt en ook nog zonder fan.

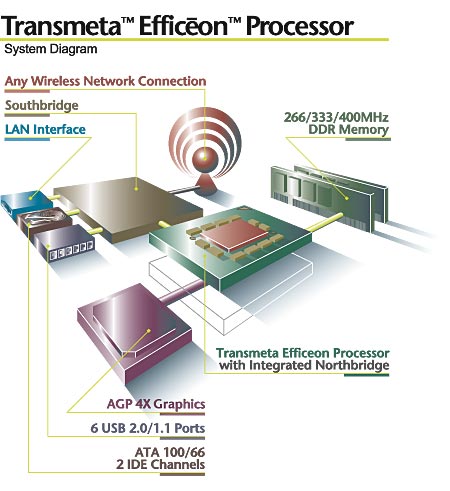

Wat ook al duidelijk was geworden is dat de Efficeon HyperTransport gaat gebruiken. Nog onbekend was welk geheugen in combinatie met deze processor toegepast kan worden. Dat is minimaal DDR266 tot maximaal DDR400 SDRAM geworden, met ECC-ondersteuning als optie. Daarnaast maakt de toepassing van een geïntegreerde northbridge het mogelijk om goedkoper en kleiner te produceren. Zo meet de oppervlakte van de Efficeon TM8820 21mm², terwijl de nVidia nForce3 Go 120-southbridge ook klein van stuk is: 22mm². De standaard Efficeon TM8600 zal 29mm² aan oppervlakte meten, dankzij ondermeer het 130nm-productieproces.

Transmeta hoopt dat deze energiezuinige processor zijn weg zal gaan vinden in handhelds, pc's en servers. Verder zal de Efficeon dankzij zijn specificaties en prestaties een grote concurrent van de Intel Pentium-M kunnen worden. Deze concurrentie met de Pentium-M zal verder in 2004 worden uitgebreid met de introductie van een 2GHz-processor in 2004. Hoewel deze dan wel 25Watt zal gaan gebruiken, maar de grootte zal waarschijnlijk niet toenemen omdat er dan op 90nm worden gebakken. Voor 2005 legt Transmeta de lat wat betreft het productieprocédé wat hoger, of liever gezegd wat kleiner, aangezien de roadmap dan van een 65nm Efficeon-processor spreekt. In eerste instantie zal de 130nm Efficeon worden geproduceerd door TSMC, waarna medio 2004 Fuji dus de 90nm 2GHz-processors gaat produceren.