Als alles volgens plan verloopt, krijgt Europa in de komende jaren een heuse exascale-supercomputer. Niet alleen moet dat systeem op dat moment behoren tot de krachtigste supercomputers ter wereld, maar deze high-performance computing-machine moet ook gebaseerd worden op high-end chips die in Europa zijn ontworpen. Dat is opvallend; momenteel gebruiken de meeste supercomputers chips die in de VS of Azië zijn ontwikkeld door grote en gevestigde bedrijven. Denk bijvoorbeeld aan chipgiganten als AMD, Intel of Nvidia.

De EU hoopt echter onafhankelijk te worden van dergelijke technologieën uit andere regio's en zette daarom een aantal jaar geleden het European Processor Initiative op. Binnen dat initiatief werken verschillende Europese bedrijven en onderwijsinstellingen samen aan het ontwikkelen van een nieuwe generatie processors en accelerators voor high-performance computing-doeleinden, bijvoorbeeld voor gebruik in dergelijke exascale-supercomputers, maar ook in servers, auto's en andere domeinen.

Onlangs werden voor het project de eerste RISC-V-testaccelerators in ontvangst genomen, waarmee het project zijn eerste concrete stappen richting Europese hpc-hardware heeft gezet. Een mooie gelegenheid om het European Processor Initiative uit te lichten. Want wat is het EPI precies? Hoe gaat het te werk? Waar staat het nu en wat wil men er precies mee bereiken?

Wat is EPI?

Het European Processor Initiative kreeg in 2018 het startschot van de Europese Commissie en is opgezet als een consortium dat momenteel 28 bedrijven, universiteiten en andere partners uit tien verschillende Europese landen omvat. Het doel van het project is het ontwerpen en uitbrengen van Europese hpc-chips, die op termijn kunnen worden gebruikt in Europese exascale-supercomputers, datacenters of de automotive-industrie. Het consortium werkt daarvoor onder andere aan een general purpose processor, RISC-V-accelerators en een common platform waarmee bedrijven hun eigen cores of accelerators in deze chips kunnen integreren.

Uiteindelijk moet het project leiden tot een commercieel ecosysteem voor Europees chipontwerp. Daarmee hoopt de EU onafhankelijk worden van andere regio's. Dat is iets wat momenteel ontbreekt in Europa; er zijn wel gevestigde chipontwerpers actief in de regio, maar die maken geen hpc-chips.

"Met EPI willen we een basis creëren van ontwikkelaars en mensen die begrijpen hoe het ontwerpen van krachtige chips met laag stroomverbruik in elkaar steekt. Mensen die weten hoe ze zulke chips kunnen maken en hoe ze die commercieel kunnen exploiteren", vertel Mario Kovač aan Tweakers. Kovač is chief communications officer van EPI en director van het HPC Architectures and Applications Research Center aan de Universiteit van Zagreb.

"Om dit te bereiken, hebben we een pad uitgestippeld met doelen voor op de korte en op de langere termijn. Helemaal vanaf nul beginnen is simpelweg niet realistisch, dus om binnen een redelijke termijn iets op de markt te brengen, hebben we de Arm-architectuur uitgekozen voor onze eerste generatie general purpose processor, gecombineerd met enkele van onze eigen ontwerpen daar bovenop." Op de langere termijn wil EPI een aantal van die externe IP's in zijn chips vervangen met eigen Europese ontwerpen. EPI werkt ook aan accelerators, waarbij het bijvoorbeeld de RISC-V-architectuur als veelbelovend ziet.

EPI is uiteindelijk in de steigers gezet om strategische redenen. De Europese Commissie schreef bij de aftrap in 2018 over het initiatief: "EPI maakt deel uit van een bredere strategie om een onafhankelijke Europese hpc-industrie te ontwikkelen." Dat is niet verrassend. Dit high-performance computing-segment, waaronder bijvoorbeeld supercomputers, datacenters en edge computing vallen, wordt steeds belangrijker en dat zal in de komende jaren enkel toenemen.

Gelet op geopolitieke spanningen in de afgelopen jaren, zet Europa dan ook op meerdere technologische fronten in op onafhankelijkheid, waaronder geavanceerde chipproductie. Voor dit specifieke project trekt de EU bijna 80 miljoen euro uit voor de eerste fase van EPI. Die subsidie zijn verdeeld onder de verschillende deelnemers, voor de ontwikkeling van hun afzonderlijke componenten en IP's die in de uiteindelijke chips moeten worden gebruikt.

De werkwijze

Om de eerdergenoemde doelen te behalen, hebben de deelnemers van EPI verschillende streams opgezet die zich ieder op een eigen domein richten. Zo richt een van de streams zich bijvoorbeeld op de eerdergenoemde general purpose processor, ofwel gpp, die bedoeld is voor hpc-toepassingen. De eerste generatie hiervan staat in de planning voor volgend jaar en voor die versie gebruikt het consortium Neoverse-hpc-cores van Arm.

Diezelfde gpp-stream werkt daarnaast aan een common platform. Daarmee wil EPI de algemene specificaties van de architectuur beschikbaar maken, naast een ontwerpmethodologie om chips te maken die werken met de processors van EPI. Zo kunnen andere bedrijven hun eigen technologieën en accelerators integreren in de uiteindelijke chips van het initiatief.

"Het idee van het common platform is om de globale architectuur in de toekomst beschikbaar te maken voor kleinere bedrijven, zodat ze hun eigen cores in onze processors kunnen integreren; iets dat ze wellicht niet zelfstandig kunnen doen vanwege de ontwikkelingskosten, productiekosten of know-how, of om andere redenen", vertelt Kovač.

Parallel daaraan heeft EPI een andere stream, die zich specifiek richt op accelerators. Daarvoor gebruiken de EPI-deelnemers de opensource RISC-V-instructiesetarchitectuur. Dergelijke accelerators zijn bedoeld om specifieke rekentaken of werklasten uit te voeren en kunnen uiteindelijk de gpp aanvullen in toekomstige chips.

De keuze van RISC-V is een logische; het is een opensource-instructiesetarchitectuur, waardoor iedereen hem naar wens mag gebruiken om chips mee te ontwikkelen. Gebruikers kunnen de RISC-V-isa zelf bovendien uitbreiden, bijvoorbeeld door extensies voor bepaalde werklasten toe te voegen. EPI schrijft zelf verder dat de open aard van RISC-V ook helpt om niet-Europese gepatenteerde technologieën te omzeilen. Tweakers publiceerde eerder al een achtergrondverhaal over de opkomst van RISC-V.

/i/2004654252.png?f=imagenormal)

Een andere EPI-stream is gerelateerd aan de automotive-markt. In die stream werken EPI-deelnemers aan chips die geïntegreerd kunnen worden in auto's. "De level 4- en level 5-auto's zijn minder auto dan computer. In de toekomst gaat dat alleen nog maar toenemen", vertelt Kovač. "Ze hebben echt high-end processors nodig die alle beeld- en radargegevens kunnen verwerken en daarbovenop AI-algoritmes kunnen toepassen om de omgeving van de auto daadwerkelijk te begrijpen. Voor die auto's zijn oudere processors niet meer goed genoeg."

"Die chips zouden dus bedoeld zijn voor in een auto. Daar zit je met stroomproblemen, omdat je niet te veel stroom kunt verbruiken in een auto, maar wel een hoop data moet verwerken. Dat is een voorbeeld van een toepassing waarbij een teruggeschroefde versie van onze general purpose-processor interessant zou kunnen zijn."

De huidige stand van zaken: EPI's eerste testchips

Het EPI-project beslaat meerdere fasen. De eerste daarvan duurde drie jaar en wordt in de komende maanden afgerond. In dit eerste stadium heeft het project onder andere gewerkt aan zijn roadmap, en werkte het consortium aan het produceren van zijn eerste testaccelerators, een testplatform om deze chips te valideren en een automotive proof-of-concept.

Bijna drie jaar na de aftrap van het project nam EPI recent ook de eerste samples van zijn EPAC 1.0-accelerators in ontvangst. Daarop zijn inmiddels de eerste tests succesvol uitgevoerd op een testplatform dat eveneens is ontwikkeld door EPI-deelnemers.

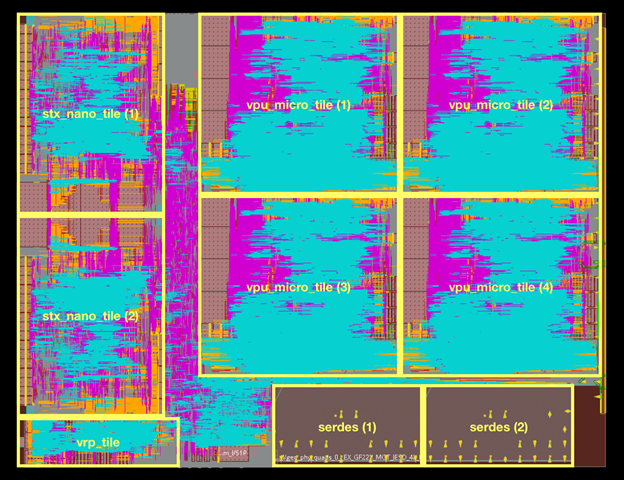

De eerste EPAC-testchips bestaan uit meerdere accelerators die bedoeld zijn verschillende toepassingen. De chips beschikken over vier vector processing-microtiles die op hun beurt bestaan uit een Avispado-RISC-V-core van deelnemend bedrijf SemiDynamics, naast een vector processing-unit van het Barcelona Supercomputing Center en de Universiteit van Zagreb.

Deze tiles beschikken ook over L2-cache en een home node die het geheugensubsysteem in kaart brengt. Daarbuiten beschikt EPAC 1.0 over stx-accelerators die zijn bedoeld voor het versnellen van stencil- en deep learning-berekeningen, en een variable precision processor. Dit alles wordt met elkaar verbonden middels een network-on-chip en SerDes-technologie van Extoll. Deze afzonderlijke onderdelen worden geleverd door verschillende deelnemers van het EPI en zijn op de chip samengevoegd.

De EPAC 1.0-samples vormen een belangrijke eerste stap voor het EPI op weg naar zijn Europese hpc-hardware, maar desalniettemin zijn het vooralsnog alleen testchips. EPI werkt bovendien al aan nieuwe versies van zijn EPAC-accelerator. "Die zullen niet dit jaar komen, maar we werken aan een aantal redesigns", vertelt Kovač aan Tweakers. "Voordat we daadwerkelijk veranderingen doorvoeren, willen we echter eerst testen wat we nu hebben. Op basis van die tests kunnen we enkele wijzigingen in de architectuur aanbrengen, of juist dingen behouden als ze naar behoren werken."

EPI onderzoekt daarnaast de mogelijkheden voor chiplets in zijn EPAC-accelerators en wil andere nodes gebruiken voor toekomstige versies van deze chip. De EPAC 1.0-samples worden geproduceerd op een 22nm-procedé van GlobalFoundries, maar op termijn wil het consortium overstappen op 12nm-nodes of kleiner. "Het plan is om uiteindelijk over te gaan op die meer geavanceerde procedés. Maar nogmaals, we willen er zeker van zijn dat de functionaliteit en prestaties van de architecturen aan de verwachtingen voldoen, voordat we veel geld uitgeven aan dure productie op die echte high-end technologieën."

:strip_exif()/i/2004672864.jpeg)

Rhea-chips met Arm-cores en RISC-V-accelerators

Met de levering van de EPAC 1.0-samples is de eerste fase van het project bijna afgerond. Voor later dit jaar staat alleen nog het eerder genoemde automotive proof-of-concept in de planning. "Dat project wordt momenteel afgerond. Het idee is dat we een daadwerkelijke auto bouwen die over enkele van onze platformen beschikt. Die auto moet de beeld- en radargegevens en alle andere data kunnen verwerken, en hij moet berekeningen kunnen maken en beslissingen kunnen nemen. Daar horen jullie de komende maanden meer over."

Volgend jaar gaat fase twee van het initiatief van start, waarin het project wordt voortgezet onder de EuroHPC-joint undertaking. In deze fase wil EPI onder andere de commerciële release van zijn eerste EPI-chips bewerkstelligen. Daaronder valt bijvoorbeeld een eerste generatie general purpose processors, die worden ontwikkeld door EPI-deelnemer SiPearl. Deze chips dragen de codenaam 'Rhea'. Ze maken gebruik van Arm Neoverse V1-cores, oftewel 'Zeus'. Deze cores werden in april geïntroduceerd door Arm en zijn speciaal bedoeld voor hpc-toepassingen, bijvoorbeeld voor gebruik in supercomputers of datacenters.

De Rhea-chips worden aangevuld met RISC-V-accelerators, hoewel nog niet duidelijk is in welke opstelling dat zal gebeuren. "Ik kan de precieze eindconfiguraties van de chips niet delen, omdat daar nog aan wordt gewerkt. Tot op de laatste dag voordat we het ontwerp opsturen voor productie, kunnen we nog beslissen om veranderingen aan te brengen in de architectuur", zegt Kovač.

Wel bekend is dat EPI de general purpose processors zal produceren op het 6nm-procedé van TSMC, oftewel N6. Vorig jaar plaatste een Franse politica op Twitter een diagram van de Rhea-chip dat wees op een processor met 72 Neoverse V1-cores, hoewel het mogelijk is dat dit voor release ook wordt gewijzigd.

/i/2004667478.png?f=imagearticlefull)

Omwille van tijd worden deze gpp's en accelerators verder gecombineerd met IP's van externe leveranciers, die niet per se Europees zijn. "We hebben het daar niet alleen over de Arm-architectuur, maar je hebt bijvoorbeeld ook wat netwerkcontrollers, wat geheugen, clock generators, gates ... dingen die wereldwijd beschikbaar zijn bij verschillende leveranciers. We proberen daarmee tijd te winnen."

"Dit is overigens niet echt uit strategische overwegingen", vervolgt Kovač. "Het is meer praktisch. We bekijken hoe we de chip zo snel mogelijk op de markt kunnen brengen. We proberen redelijk te zijn; we kunnen niet alles vanaf nul ontwerpen. In de toekomst zouden we wel kunnen beslissen om sommige van die dingen zelf te ontwikkelen."

EPI was aanvankelijk van plan om zijn Rhea-generatie in 2021 uit te brengen, maar de chips hebben eerder al zeker een jaar vertraging opgelopen. Deze processors staan nu op de roadmap voor 2022, hoewel dat ook nog niet volledig in kannen en kruiken lijkt. "We kijken naar een release in 2022, maar je weet wat er allemaal speelt in de halfgeleidersector. We hopen dat we alles volgens plan kunnen uitvoeren."

De toekomstplannen van EPI: nieuwe generaties chips en hpc-machines

Met de release van Rhea brengt EPI zijn eerste echte commerciële chips op de markt. Vervolgens is het plan om zijn zelfontwikkelde IP's beschikbaar te maken voor anderen. Daarvoor dient het Launch Pad, wat in 2022 of 2023 moet worden afgetrapt. Dat Launch Pad is volgens Kovač een platform om de producten van EPI te commercialiseren.

"Het idee vanuit Europa was niet om het zoveelste onderzoeksproject te starten."

"We zouden graag sommige van onze IP's of RISC-V-chips commercieel aanbieden aan derde partijen, en Launch Pad is onze naam daarvoor. Daarmee kunnen we onze ontwerpen uitbrengen voor andere bedrijven die ze vervolgens in hun eigen chips kunnen verwerken. Dat is dus het idee erachter; om echt een industrie rond dit initiatief te ontwikkelen. Het idee vanuit Europa was niet om het zoveelste onderzoeksproject te starten. We proberen er commerciële producten van te maken die in Europa en de rest van de wereld kunnen worden gebruikt."

In de tussentijd blijft EPI aan nieuwe chips werken. Als alles volgens de huidige plannen verloopt, moeten de tweede generatie Cronos-gpp's van SiPearl de Rhea-chips in 2023 of 2024 opvolgen. "Dat is momenteel nog niet helemaal vastgelegd," vertelt Kovač. "Maar de volgende generatie wordt, net als bij alle andere bedrijven, een beter product met betere features en hopelijk ook een grotere markt en grotere klantenkringen. Tegen die tijd weten hoe onze RISC-V-chips presteren en we zullen zien wat er met de Arm-architectuur gaat gebeuren, gelet op de mogelijke overname door Nvidia. We gaan na de eerste generatie ook bekijken wat de nichemarkten zijn waar we ons kunnen verbeteren."

In de komende periode wil het consortium zijn chips ook testen in pilotsystemen. De Europese Commissie heeft daarvoor twee pilots goedgekeurd, die volgens Kovač in de komende maanden al beginnen. "Het idee achter die pilots is om onze ontwikkelde technologieën te gebruiken en daarmee daadwerkelijk machines te bouwen. Zo kunnen we aantonen dat niet alleen de processors zelf werken, maar dat het systeem eromheen ook commercieel bruikbaar is."

Een van die twee pilots is gebaseerd op de Rhea-generatie chips, waarmee EPI een systeem wil bouwen en de prestaties ervan wil tonen. "De tweede pilot is gebaseerd op RISC-V-accelerators en kun je eerder zien als een 'ontwikkelingsvoertuig'. Het zullen geen higher-end chips worden, omdat RISC-V momenteel nog niet volwassen genoeg is. Maar die pilot zal wel softwareontwikkeling en co-ontwerp faciliteren."

Op weg naar exascale-machines

Het uiteindelijke doel is echter nog altijd het bouwen van een exascale-supercomputer met Europese processors, zoals eerder vermeld. Daarover zijn momenteel nog weinig concrete details bekend, maar gelet op het tijdsbestek zal deze machine naar verwachting gebruikmaken van de Cronos-chips van EPI.

Ruim twee jaar geleden sprak Leonardo Flores van de Europese Commissie tijdens het HPC User Forum al zijn hoop uit dat de Cronos-chips 'uiterlijk 2023' geïntegreerd kunnen worden in de eerste Europese exascale-machines. Kovač kon niet concreet reageren op het tijdsbestek voor deze eerste exascale-machine, hoewel hij wel het eerdere uitstel in de roadmap erkent. Tegelijkertijd staat Cronos momenteel op de EPI-roadmap voor 2023 of 2024; in dat tweede scenario zou een exascale-machine met Cronos-chips dus op zijn vroegst in 2024 verschijnen.

Al met al laten de eerste Europese exascale-machines nog zeker een paar jaar op zich wachten, uitgaande van de huidige planning. Dat is ook niet gek, aangezien Europa drie jaar geleden eigenlijk vanaf nul is begonnen aan het EPI. Op het moment van schrijven zijn er überhaupt nog geen exascale-supercomputers actief, ook niet met chips van gevestigde bedrijven als AMD, Intel en Nvidia. De eerste exascale-supercomputer, Frontier, komt later dit jaar pas online, in de VS. De exascale-plannen van EPI zijn dan ook erg ambitieus, zelfs na het eerdere uitstel, en de haalbaarheid daarvan binnen het gegeven tijdsbestek moet in de komende jaren nog blijken.

Strategisch belang

Zoals eerder vermeld, moet EPI uiteindelijk ook leiden tot een Europees ecosysteem van bedrijven die chips ontwerpen. "Dat is een traag proces", vertelt Kovač. "Het vereist langdurige toewijding van alle betrokkenen, met inbegrip van de politiek, chipontwerpers en het onderwijssysteem." Volgens Kovač en EPI is dat belangrijk, met oog op het eerdergenoemde strategische belang dat Europa waarneemt in de chipindustrie. "We hebben in de afgelopen jaren gezien hoe geopolitiek de industrie echt kan beïnvloeden, en vooral in de huidige digitale wereld waar alles draait om data, kan dat heel lastig zijn","Het is een langzaam proces. Het vereist langdurige toewijding van alle betrokkenen."

vertelt Kovač.

"Europa doet het erg goed op het gebied van softwareontwikkeling, maar op het gebied van hardware hebben we te lang op buitenlandse technologie vertrouwd. Strategisch gezien verwerken we steeds meer data en sommige daarvan zijn erg gevoelig. Je wil dan niet alleen afhankelijk zijn van andere bronnen, die mogelijk niet altijd beschikbaar zijn wanneer je ze nodig hebt."

Beeld: gorodenkoff / Getty Images

:strip_icc():strip_exif()/i/2008000650.jpeg?f=fpa_thumb)

/i/2004987058.png?f=fpa_thumb)

:strip_icc():strip_exif()/i/2004921950.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2004924204.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2004394948.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2004086480.jpeg?f=fpa_thumb)

/i/2007820604.webp?f=fpa)

:strip_exif()/i/2007714636.jpeg?f=fpa)

:strip_exif()/i/2005134784.jpeg?f=fpa)

:strip_exif()/i/2004959200.jpeg?f=fpa)

:strip_exif()/i/2004917882.jpeg?f=fpa)

/i/2004779058.png?f=fpa)

/i/2004607452.png?f=fpa)

/i/2004636488.png?f=fpa)

/i/2004742420.png?f=fpa)

/i/2004720370.png?f=fpa)

/i/1187273135.png?f=fpa)

/i/1241008580.png?f=fpa)

:strip_exif()/i/1045165316.gif?f=fpa)

/i/2003553410.png?f=fpa)