Inleiding: op naar de ångström

Het Vlaamse onderzoeksinstituut Interuniversitair Micro-Elektronica Centrum, kortweg imec, werkt samen met diverse bedrijven, zoals Intel, Samsung en GlobalFoundries, onder meer aan de ontwikkeling van cmos-technologie. Het instituut is gehuisvest in Leuven en werkt samen met de lokale universiteit, maar ook met researchcentra in Taiwan, de Verenigde Staten, Japan en Nederland. Het imec houdt jaarlijks een evenement, het Imec Technology Forum, waarop de stand van zaken op technologisch gebied uiteen wordt gezet, en dan natuurlijk vooral op de vlakken waarop het imec en zijn partners onderzoek doen.

Een van de belangrijkste onderzoeksgebieden van het imec en zijn partners is de halfgeleiderindustrie, en dan in het bijzonder het ontwikkelen van steeds kleinere cmos-technologie. Bij het imec wordt aan technologie gewerkt die enkele jaren tot zo'n tien jaar in de toekomst moet worden ingezet en een van de interessantste en meest informatiedichte presentaties op dit gebied is die van imecs evp halfgeleidertechnologie An Steegen.

/i/2001550817.png?f=imagenormal) Een van de opvallendste elementen in haar presentatie was een grafiek met transistorscaling in de komende jaren. Momenteel bevinden we ons in de transitieperiode van 14 naar 10nm, maar op de kaart stonden bekende kleinere nodes als 7, 5 en zelfs 3 en 2nm. De node daarna, gepland voor introductie rond 2025 of 2026, spreekt echter niet meer van nanometers, maar van ångström, een eenheid die normaal gesproken gereserveerd is om individuele atomen te beschrijven. Op de roadmap is sprake van een 14A-node, wat overeenkomt met 1,4nm, aangezien één ångström 0,1nm is.

Een van de opvallendste elementen in haar presentatie was een grafiek met transistorscaling in de komende jaren. Momenteel bevinden we ons in de transitieperiode van 14 naar 10nm, maar op de kaart stonden bekende kleinere nodes als 7, 5 en zelfs 3 en 2nm. De node daarna, gepland voor introductie rond 2025 of 2026, spreekt echter niet meer van nanometers, maar van ångström, een eenheid die normaal gesproken gereserveerd is om individuele atomen te beschrijven. Op de roadmap is sprake van een 14A-node, wat overeenkomt met 1,4nm, aangezien één ångström 0,1nm is.

Hoe het imec en consorten denken in de komende jaar of acht te schalen naar transistors met afmetingen in de orde van grootte van ångströms, zullen we in de komende pagina's nader bekijken. Daarnaast kijken we naar de technologie die mogelijk wordt gemaakt door de alsmaar geavanceerdere halfgeleiderindustrie, en welke randvoorwaarden en toepassingen er zoal zijn.

Euv: bij 7 of bij 5nm?

Inmiddels hebben de meeste grote chipfabrikanten, denk aan Intel, TSMC en Samsung, hun plannen voor chipproductie rond 10nm bekendgemaakt. Hoewel de naamgevingen van hun respectievelijke nodes niet altijd een-op-een te vergelijken zijn, komen Intel, Samsung, TSMC en GloFo binnen nu en anderhalf jaar op nodes van zo'n 9 tot 10nm. Dat gebeurt nu nog met traditionele lithografische technieken, maar tegen zeer hoge kosten. Dat blijft niet haalbaar voor kleinere nodes, want dan zouden veel te veel dure stappen nodig zijn om een wafer te verwerken.

Zoals we eerder hebben beschreven, moet een wafer belicht worden om er structuren op te krijgen, maar de huidige 193nm-immersielithografie, vaak afgekort tot 193i, vergt voor kleinere structuren verschillende belichtingsstappen en dus verschillende maskers. Dat is extreem duur en duurt bovendien lang, temeer omdat voor een complete wafer meestal tientallen lagen nodig zijn. Om nog kleinere transistors te maken, vanaf 7nm en daar voorbij, zou double- of triple-patterning niet meer genoeg zijn, maar zou zelfs vier keer belicht moeten worden. Daarom zou euv, de langbeloofde en veelvuldig uitgestelde belichtingstechniek met een veel kortere golflengte van slechts 13,5nm, uitkomst moeten brengen.

/i/2001550867.png?f=imagenormal)

Volgens het imec zou de 7nm-node een geschikt 'insertion point' voor euv-lithografie zijn. Euv zou dan het aantal belichtingsstappen reduceren naar slechts één, wat de kosten van chips moet drukken. Daarbij zou euv overigens niet voor elke laag ingezet hoeven te worden, maar slechts voor enkele kritische stappen in het productieproces. Dat moet, afhankelijk van de fabrikant, in de loop van 2018 of later plaatsvinden. GlobalFoundries zou in 2019 in zijn New York-fab euv gaan inzetten en ook Samsung zou euv voor zijn 7nm-node inzetten, met een verwachte introductie in 2019. Voor Intel zou het maar zeer de vraag zijn of het euv inzet voor de 7nm-node; waarschijnlijker is dat het bedrijf wacht tot de 5nm-node, een tactiek die ook TSMC lijkt te volgen.

Voor de succesvolle inzet van euv-lithografie moeten nog altijd enkele hordes genomen worden, hoewel de belangrijkste daarvan, de waferdoorvoersnelheid, aardig op orde lijkt. Inmiddels kunnen ruim honderd wafers per uur belicht worden en kunnen structuren met 26nm afstand tussen de horizontale lijnen geëtst worden. Het masker waar het euv-licht doorheen moet schijnen, moet beschermd worden tegen onder meer stof, maar zo'n beschermingslaagje of pellicle moet niet alleen euv-doorlatend zijn, maar ook bestand tegen hitte. ASML werkt aan polysilicon-pellicles, maar het is de vraag of die bestand zijn tegen de hitte én of ze op tijd klaar zijn. Het imec werkt aan een alternatieve techniek op basis van koolstofnanobuisjes, die pellicles moet opleveren die 97 procent van het euv-licht doorlaten en bijzonder sterk zijn.

/i/2001550865.png?f=imagenormal)

Een ander knelpunt is de fotoresistlaag, die bij euv-lithografie uiteraard een andere samenstelling moet hebben dan bij 193i. Groot probleem daarbij is de korreligheid van de resulterende structuren op de wafer. Door de resist zorgvuldig samen te stellen en de belichte wafers chemisch na te behandelen, kunnen de lijnen en kritische dimensies inmiddels goed worden 'afgedrukt', met variaties van slechts enkele nanometers. De featureafmetingen die momenteel gerealiseerd kunnen worden, bedragen 13nm voor de half pitch tussen lijntjes en 18nm tussen gaten voor via's.

Nieuwe typen transistors en ontwerpfilosofie

Het euv-proces lijkt dus langzaam maar zeker onder de controle van chipfabrikanten te komen, maar met een procedé voor chipproductie ben je er nog niet. De grote vraag is natuurlijk, wat moet je maken? Finfets, zoals die momenteel in de logica worden toegepast, kunnen niet eeuwig gebruikt blijven worden. Een van de grote krachten van finfets wordt gevormd door, je raadt het al, de fins of ribben van de transistor. Hoe groter die ribben en hoe meer ervan zijn, des te beter een finfet kan presteren dankzij het grotere contactoppervlak tussen gate en channel. Bij kleinere nodes kunnen minder ribben in finfets gebruikt worden, zodat de voordelen van finfets langzaam verdwijnen. Zo kunnen bij 10nm-finfets twee transistors met drie ribben gebruikt worden, maar bij 7 en 5nm zouden nog maar twee finfets met twee ribben gebruikt kunnen worden, doordat er gewoonweg minder ruimte is.

/i/2001550869.png?f=imagenormal)

Daar zit een mogelijkheid voor euv. In 10nm-finfets worden zogeheten seven-track-libraries gebruikt, die drie finfets per cel mogelijk maken. Als immersielithografie gebruikt blijft worden, daalt dat bij 5nm naar twee en bij 3nm naar één finfet. Met euv-lithografie zouden de tracks verkleind kunnen worden, zodat op 5nm nog steeds een five-track-library gebruikt kan worden, met twee finfets met ieder twee ribben. Pas bij de 3nm-node zou dan naar een ontwerp met slechts één finfet overgestapt hoeven te worden en op dat moment zouden de prestaties van een finfet ongeveer gelijk zijn aan die van een transistor met nanodraden als channel. De nanodraden zouden wel als voordeel hebben dat ze betere scaling mogelijk maken, want binnen een enkele rib zouden verscheidene nanodraden als gate/channel dienst kunnen doen door ze te stapelen binnen de ribben. Bij het imec hebben onderzoekers zo al finfets met acht nanodraden gemaakt.

Het alternatief voor finfets op 3nm zouden 'pinched finfets' zijn, wat in essentie als een nanowire omschreven wordt. De gate zit dan volledig om het channel heen, wat weer betere elektrostatische eigenschappen met zich meebrengt. Een enkele rib met daarin een nanowire zou daardoor kleiner kunnen zijn, zodat transistors kleiner kunnen worden gemaakt. Door verschillende nanowires in een rib onder te brengen, kunnen chipmakers de prestaties verder verbeteren. Als proof-of-concept zijn inmiddels al transistors met acht nanodraden gebouwd en ook het gebruik van germaniumnanodraden of ovale nanodraden van III-V-halfgeleiders, die nanosheets genoemd worden, zou de prestaties van 3nm-transistors verbeteren.

/i/2001550873.png?f=imagenormal)

Na de 3nm-node zou de 2nm-node volgen en daarvoor is zelfs euv in zijn huidige incarnatie niet geschikt. De printafmetingen van lithografie zijn onder meer afhankelijk van de gebruikte golflengte en hoe goed die kan worden gericht door een lenzenstelsel. Voor 2nm zou de numerieke apertuur van de lenzen omhoog moeten om uiteindelijk bij de volgende node aan te komen. Die wordt niet meer in nanometers gemeten, maar in ångströms, tienden van nanometers. Hoe die node er precies uit moet gaan zien, met wat voor soort transistors en materialen, is nog onduidelijk, maar voor de halfgeleiderindustrie is scaling, het kleiner maken van transistors, nog lang niet dood.

3d-technieken en materialen

Toch zouden kleinere transistors in chips niet de enige methode zijn om zuinigere en snellere chips te bouwen. In plaats daarvan moeten procedés, materialen en ontwerpen hand in hand met elkaar worden ontwikkeld om voor elke toepassing tot een optimale mix te komen. Zo kunnen socs worden ontwikkeld waarin verschillende soorten transistors voor verschillende taken worden ingezet. In bijvoorbeeld de gpu, waar parallellisatie en dus zoveel mogelijk rekeneenheden in een kleine ruimte, belangrijk zijn, kunnen nanodraadtransistors worden gebruikt. In de cpu-cores daarentegen, waar snelheid en rekenkracht nodig zijn, zouden de finfets nog steeds ingezet worden, maar dan zo klein mogelijk natuurlijk. De caches, opnieuw een blok waar hoge dichtheid vereist is, kunnen met mram worden opgebouwd.

/i/2001550875.png?f=imagenormal)

Zo'n hybridisatie kan gerealiseerd worden door heterogene halfgeleidertechnologie op een die te integreren, maar een andere optie kan 3d-stacking zijn. Dat zou waarschijnlijk goedkoper zijn, doordat alle verschillende technieken op een eigen wafer gemaakt kunnen worden, maar het stacken en onderling verbinden van de dies in een 3d-structuur zou een hoge mate van precisie van interconnects als tsv's vergen. Een derde methode zou het sequentieel vervaardigen van een die met verschillende technieken zijn, waarbij de ene transistortechniek boven op de andere wordt geproduceerd. Daarbij is de warmteontwikkeling een lastig punt, niet alleen tijdens bedrijf, maar ook tijdens productie. Veel lithografiestappen worden immers bij hoge temperatuur uitgevoerd.

Ultrapuur

Hand in hand met de ontwikkeling van nieuwe transistors moeten ook nieuwe materialen ontwikkeld worden. Waar, kort door de bocht, vroeger een plaat silicium voldeed, zijn nu allerlei materiaalinnovaties nodig om chips te produceren. Een van de bekendste van recente tijden is waarschijnlijk hafniumoxide, dat door onder meer Intel werd ingezet als gate-isolatie, als vervanger voor siliciumoxide. Zo is eigenlijk elke nieuwe node mede mogelijk gemaakt door een verandering in de gebruikte materialen, van strainded silicium tot toekomstige koolstofnanobuizen. Niet alleen de transistors zelf vergen nieuwe materialen. Ook voor de procedés zijn steeds geavanceerdere materialen nodig. Denk maar aan de fotoresistchemicaliën zoals die voor euv ontwikkeld worden. Voor 193i-lithografie worden ArF-lasers gebruikt die argon en fluor nodig hebben en in een fab worden duizenden kubieke meters ultrapuur stikstofgas gebruikt.

Voor de eeuwwisseling werden slechts zo'n tien verschillende materialen gebruikt voor de productie van een chip. Inmiddels is dat gegroeid tot zo'n honderd chemicaliën. Bovendien zijn de gebruikte hoeveelheden van elk materiaal kleiner geworden, maar de prijzen zijn ruim vertienvoudigd. Dat is niet zo gek als je bedenkt dat de structuren op een wafer veel kleiner zijn geworden. Dat vergt veel puurdere materialen, want een verontreiniging in de vorm van een ander materiaal in een mengsel heeft een veel grotere impact. Ter illustratie, de meeste mensen zijn bekend met luchtverontreinigingen die in de orde van ppm of parts per million worden gemeten. Verontreinigingen worden door de halfgeleiderindustrie echter in ppq gemeten, ofwel parts per quadrillion, één deeltje op 1.000.000.000.000.000 deeltjes.

Geheugen wordt magnetisch

We tipten bij de neuromorfische systemen al even nieuwe geheugentypen aan als reram, mram en oxram, maar over de hele linie van geheugens wordt aan verbeteringen gewerkt. Zo werd geheugensnelheid tegen capaciteit afgezet, met harde schijven als langzame exponent met hoge capaciteit en sram-cellen als kleine geheugens met hoge snelheid. Dat sram wordt bijvoorbeeld als L1-cache voor processorcores ingezet. Traditioneel zijn de belangrijkste typen geheugen hdd, flash, dram en sram. Daar is niet zo lang geleden scm of storage class memory bijgekomen, denk aan Intels 3d-Xpoint-geheugen.

Er wordt echter hard gewerkt aan nieuwe technieken, zoals spin orbit torque-ram, spin transfer torque-mram en 3d-sram voor de snelle, kleinere geheugens. Daarnaast wordt gewerkt aan onder meer fefet, een afkorting voor ferro-electric fets, phase change-memory, reram of resistive ram en natuurlijk steeds meer lagen 3d-nand.

/i/2001550887.png?f=imagenormal) Voor caches met sram worden over het algemeen ontwerpen met zes of acht transistors gebruikt en in het verleden schaalde de oppervlakte ongeveer zestig procent per node. Vanaf vijf nanometer en daar voorbij zou een oppervlaktereductie van 0,6x met finfet-transistors echter behoorlijk lastig worden, reden om naar alternatieve transistortechnologie te zoeken. Zo worden voor sram onder meer cfets, of complementary fets ontwikkeld, waarbij een n-fet boven op een p-fet wordt gebouwd. Ook vfets, of vertical fets met p-fets naast n-fets, worden ontwikkeld, waarbij de source en drain boven elkaar zitten met gates en channels ertussen, in plaats van naast elkaar. Met vfets wordt op dezelfde node een oppervlaktereductie van dertig procent ten opzichte van gewone finfets gerealiseerd.

Voor caches met sram worden over het algemeen ontwerpen met zes of acht transistors gebruikt en in het verleden schaalde de oppervlakte ongeveer zestig procent per node. Vanaf vijf nanometer en daar voorbij zou een oppervlaktereductie van 0,6x met finfet-transistors echter behoorlijk lastig worden, reden om naar alternatieve transistortechnologie te zoeken. Zo worden voor sram onder meer cfets, of complementary fets ontwikkeld, waarbij een n-fet boven op een p-fet wordt gebouwd. Ook vfets, of vertical fets met p-fets naast n-fets, worden ontwikkeld, waarbij de source en drain boven elkaar zitten met gates en channels ertussen, in plaats van naast elkaar. Met vfets wordt op dezelfde node een oppervlaktereductie van dertig procent ten opzichte van gewone finfets gerealiseerd.

Verder wordt gewerkt aan diverse typen magnetisch ram, zoals spin transfer torque- en spin orbit torque-mram, oftewel stt-mram en sot-mram. Zo is al stt-mram gerealiseerd dat op 0,5V werkt en dan schakelsnelheden van 5ns haalt, oftewel 200MHz, genoeg voor de grotere caches. Het stt-mram kan ongeveer vier keer zo klein gemaakt worden als finfet-geheugen, maar voor L1-caches moet het geheugen sneller. Een goede kandidaat zou sot-mram zijn, waarvan de schakelsnelheid tot onder de 1ns kan dalen, naar het gigahertzbereik dus.

Voor storage class memories, zoals bekend van Intels Optane-geheugen, dat tussen dram en opslag in zit, wordt gewerkt aan nieuwe materialen voor crosspointgeheugen. Twee kruisende lijnen of elektrodes werken als een grid en waar ze elkaar kruisen, wordt een bit opgeslagen als variabele weerstand in een phase-changemateriaal als chalginogenen. Dat materiaal verandert van weerstand als het verwarmd wordt met een stroompje. Het imec heeft met stikstof verrijkte germaniumselenide-legeringen ontwikkeld die stabiel blijven bij hoge temperaturen en een aantrekkelijke kandidaat voor scm vormen.

/i/2001550889.png?f=imagenormal)

Een ander voorbeeld van geheugen met variabele weerstand is imecs oxram, dat tantalumoxidefilamenten vormt tussen twee elektrodes. De weerstand van de filamenten dient als analoge bit, met meer of minder weerstand in plaats van een logische 1 of 0. Daardoor zou het oxram goed ingezet kunnen worden met tantalumoxide als geleidend materiaal met een duidelijk verschil in hoge en lage weerstand. Bovendien zou het oxram zuinig en robuust zijn, waardoor het zeer geschikt zou zijn voor toepassingen in auto's en iot. Voor iot-toepassingen is het vooral van belang dat het geheugen tijdens lange periodes van inactiviteit zijn data behoudt zonder stroom te verbruiken en direct data paraat heeft om snel uit slaapstand te komen en kort actief te zijn, iets wat met dram niet kan.

Alternatieve systemen en geheugen

Wat als we geen traditionele computers meer maken? Alle computers, processors en socs worden nu nog met een beproefde systeemarchitectuur gemaakt: de Von Neumann-architectuur. Daarin verwerkt een centrale rekeneenheid een bepaalde invoer met behulp van onder meer verwerkings- en instructieregisters, en geheugen om instructies en data op te slaan. Het resultaat wordt teruggegeven als uitvoer. Een van de grootste problemen van die architectuur is de beperkte snelheid waarmee data tussen geheugen en cpu kan worden uitgewisseld. Dat is de reden waarom diverse caches en andere methoden worden toegepast, om toegang tot het trage geheugen zo veel mogelijk te beperken.

Het imec werkt ook aan quantumcomputers en aan

de hardware die de qubitlogica moet aansturen

Voor toekomstige systemen zou het wegnemen van die bottleneck uitkomst bieden, namelijk door geheugen en rekenvermogen te combineren tot neuromorfische of machine- danwel deep-learningsystemen. De transistors die schakelen of rekenen, zijn dezelfde als de transistors die data opslaan, waarbij een aantal geheugenarchitecturen zoals reram en mram geschikte kandidaten zijn. Dergelijke systemen werken met arrays of grids van geheugentransistorcellen die worden getraind met data. Die trainingsdata, bijvoorbeeld de letter E, leidt tot verbeterde geleiding in een kolom van zo'n array. Als nieuwe data aan het array wordt 'gevoerd', zoekt die data de kolom met de corresponderende letters, omdat die het best geleidt, en geeft daar een signaal op. Zo kunnen, in dit voorbeeld, letters herkend worden. Het imec heeft een Oxram-materiaal ontwikkeld dat hiertoe in staat is en dat met veel minder energie toekan dan een machine-learningimplementatie in traditionele hardware.

Naast Von Neumann-systemen en neuromorfische systemen zou een derde architectuur tot veel snellere berekeningen kunnen leiden, mits de data dat toelaat. Al jaren belooft quantumcomputing zeer snelle resultaten, die met traditionele rekenkracht niet of vele ordes van grootte trager berekend zouden worden. Bij het imec werkt men uiteraard ook aan quantumcomputers, maar naast de qubits die hiervoor nodig zijn, kijkt het instituut ook naar de hardware die de qubitlogica moet aansturen. Omdat quantumcomputers vooralsnog extreem gekoeld moeten worden, in de ordegrootte van enkele kelvins, moet ook de cmos-logica goed bestand zijn tegen die extreem lage temperaturen.

Het type quantumcomputers waaraan het imec werkt, is gebaseerd op silicium halfgeleiderquantumbits, waarbij finfets en nanodraden gebruikt worden om met cmos-technologie qubits te bouwen. Dankzij het gebruik van qubits zouden berekeningen met veel minder energie en veel sneller opgelost kunnen worden dan met traditionele computers, die sequentieel werken.

5g, iot en gezondheid

Naast de bekende scalingproblematiek waaraan het imec werkt, werden tijdens het ITF nog veel meer technologieën getoond. Veel daarvan kennen we natuurlijk al, zoals op het gebied van 5g en gezondheid, waar we al eerder over schreven. Dergelijke technologieën worden echter steeds vastomlijnder. Zo worden de eerste pilots met 5g inmiddels uitgevoerd en komen steeds meer gadgets, toepassingen en technieken beschikbaar voor hightechgezondheidszorg.

/i/2001550929.png?f=imagenormal)

Op het gebied van 5g worden het internet of things en vervoer meestal in één adem genoemd. Die verschillende technologieën zijn onlosmakelijk met elkaar verbonden, aangezien iot-apparaten zuinige netwerktechniek gebruiken om hun sensordata te verspreiden. Daarbij gaat het vooral om slimme sensoren voor de industrie en allerlei sensoren in steden. Voor slim vervoer, dat natuurlijk ook weer verband houdt met slimme steden, waar bijvoorbeeld verkeerslichten hun status communiceren, zijn juist het low-latencyaspect en de grote bandbreedte van 5g-verbindingen nodig. En een autonoom rijdende auto moet vanzelfsprekend communiceren met andere auto's, weggebruikers en infrastructuur, waarbij de latency in de orde van milliseconden mag zijn.

Tijdens het ITF mochten diverse sponsors onder het mom van presentaties voor eigen parochie preken, wat bedrijven als Cisco en Nokia een mooie gelegenheid bood om hun prognoses voor de aantallen connected devices te delen. Zo zouden er, afhankelijk van welke prognose je mag geloven, in 2020 zo'n 50 miljard tot 75 miljard verbonden apparaten bestaan en stijgt de omzet in de iot-industrie met honderden miljoenen euro's per jaar, met vooral voor consumenten onzichtbare toepassingen, zoals in fabrieken en steden. Toch zouden de voor consumenten relevante smarthomemarkt en wearablemarkt over enkele jaren ieder ruim vijftig miljard waard zijn.

Een punt dat hoofdbrekens oplevert, is beveiliging. Langzaamaan begint het iot-landschap wat minder wildewestentrekjes te vertonen en wordt over standaarden nagedacht, maar beveiliging moet nog meer een vast onderdeel worden, zo trachtten diverse sprekers duidelijk te maken. Een van de grootste angsten is het in het verleden al enkele malen getoonde voorbeeld van boordcomputers van auto's die gehackt worden, iets wat bij een volledig autonome verkeersstroom alleen maar gevaarlijker wordt. Maar ook de beveiliging van apparaten met biometrische maatregelen, nabijheidsensoren en ouderwetse wachtwoorden kreeg veel aandacht.

Nog belangrijker is de beveiliging van alle data die door iot-devices, auto's, over mensen en door mensen zelf geproduceerd wordt. Om de zaken extra lastig te maken moet die data, om er optimaal gebruik van te maken, ook nog gedeeld kunnen worden tussen apparaten en diensten. Het heeft immers weinig zin als een auto niet weet dat er een file op de A1 staat. Die data moet echter wel veilig gedeeld worden en niet veranderd of onderschept kunnen worden. Encryptie mag voor automotive toepassingen niet te lang duren en voor sensornetwerken niet te veel energie vergen. Bovendien moet alles gestandaardiseerd worden, zodat het naadloos kan samenwerken.

Databeveiliging geldt in nog sterkere mate in de gezondheidszorg, waar zeer privacygevoelige informatie verzameld kan worden door een groeiend aantal medische sensoren. Een extra factor is dat die data niet alleen wordt verzameld, maar ook gedeeld. Bedenk hoe moeilijk het invoeren van het EPD is en vermenigvuldig dat met enkele factoren, want met genetische data wordt het nog veel gevoeliger wat er over je bekend is. Een verzekeraar bijvoorbeeld kan nu zien dat je ziek bent, maar niet of in je genen een predispositie voor een bepaalde ziekte op latere leeftijd zit, waardoor de premie omhoog zou kunnen. Maar ook kan kankermedicatie effectiever toegepast worden als bekend is tegen welke vormen een bepaald medicijn bij anderen al effectief was. Zo hoeft het wiel niet opnieuw uitgevonden te worden en kunnen de juiste therapieën sneller en gerichter worden ingezet.

Zonne-energie en nanogrids

Naast nieuwe transistorstypen, scaling, quantumcomputers, iot en gezondheidszorg stipte deze editie van het ITF nog een ander interessant aspect aan: energie. Uiteraard wordt bij het imec volop onderzoek gedaan naar zonnecellen, waarbij vooral perovskieten de interesse van het onderzoekscentrum hebben. Met een laagje perovskiet zouden de rendementen van zonnecellen vrij goedkoop hoger worden, maar de vraag is: waar laat je die zonnepanelen? Zoals we nu doen, gewoon op het dak, levert niet genoeg oppervlakte op om aan de alsmaar toenemende vraag naar energie te voldoen. En het zijn just gebouwen, of dat nu huizen, kantoorgebouwen, fabrieken of datacentra zijn, waar de meeste energie verstookt wordt.

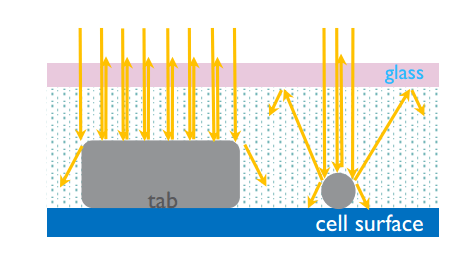

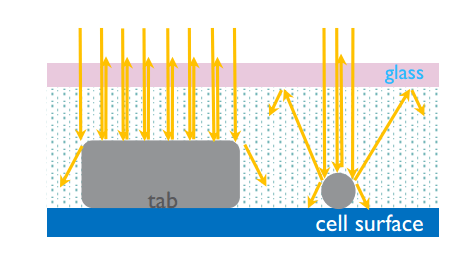

Een oplossing ligt volgens Energyville, een consortium van onder meer het imec, de universiteit van Leuven en Hasselt, in de integratie van photovoltaics in gebouwen. Doorzichtige zonnepanelen kunnen in ramen, puien en daken geïntegreerd worden. Een tactiek om dat minder opzichtig en tegelijk effectiever te maken, is het gebruik van veel dunne draden in plaats van centrale busbars om de individuele pv-cellen aan elkaar te knopen. Dat lost het kenmerkende modulaire en storende uiterlijk van zonnecellen op, en geeft de panelen een uniforme uitstraling. Die dunne bekabeling zou de productie ook goedkoper en eenvoudiger maken, omdat de interconnects als geweven doek over de modules heen gelegd kunnen worden. Elektronica als power optimizers kunnen in kozijnen worden verwerkt om dankzij korte kabels de rendementen zo hoog mogelijk te maken.

Een oplossing ligt volgens Energyville, een consortium van onder meer het imec, de universiteit van Leuven en Hasselt, in de integratie van photovoltaics in gebouwen. Doorzichtige zonnepanelen kunnen in ramen, puien en daken geïntegreerd worden. Een tactiek om dat minder opzichtig en tegelijk effectiever te maken, is het gebruik van veel dunne draden in plaats van centrale busbars om de individuele pv-cellen aan elkaar te knopen. Dat lost het kenmerkende modulaire en storende uiterlijk van zonnecellen op, en geeft de panelen een uniforme uitstraling. Die dunne bekabeling zou de productie ook goedkoper en eenvoudiger maken, omdat de interconnects als geweven doek over de modules heen gelegd kunnen worden. Elektronica als power optimizers kunnen in kozijnen worden verwerkt om dankzij korte kabels de rendementen zo hoog mogelijk te maken.

/i/2001550907.png?f=imagenormal)

Bij zonnepanelen horen ook inverters, of omvormers, die van de gelijkspanning die een zonnecel genereert, een wisselspanning te maken die compatibel is met ons elektriciteitsnet. De ironie wil echter dat vrijwel alle appraraten die we gebruiken, van die 230V wisselstroom eerst weer gelijkstroom maken. Dat levert dus twee keer transformatieverliezen op, terwijl we van dc via ac terug naar dc gaan.

Een oplossing zou de introductie van nanogrids in huizen en kantoren zijn, waar duurzame energie afkomstig van zonnepanelen of andere bronnen niet naar wisselstroom geconverteerd wordt, maar gelijkstroom blijft. In plaats daarvan wordt de wisselspanning van het stroomnet centraal in gelijkstroom omgezet en wordt de gelijkstroom van zonnepanelen daarin gemixt. Een distributienetwerk van bipolaire gelijkspanningen zou dan energie door het huis of kantoor verspreiden, waar ledverlichting, airco's, luchtcirculatieapparatuur, koelkasten en natuurlijk elektronische apparatuur als computers en aanverwante hardware er gebruik van kunnen maken.

Als apparaten van een dc-netwerk gebruik kunnen maken, kunnen adapters waarschijnlijk niet helemaal verdwijnen, maar wel een stuk eenvoudiger worden. De hele logica om van wisselstroom gelijkstroom te maken en tot veilige spanningen te reduceren, kan weggelaten worden. In die gelijkrichters en transformators wordt het meeste verlies geleden en in eenvoudigere adapters hoeft alleen een lage gelijkspanning geconverteerd te worden naar de werkspanning van het apparaat./i/2001550921.png?f=imagenormal)

Bovendien zou het eenvoudiger zijn om apparatuur zoals accu's, waaronder Tesla's Powerwall, elektrische auto's en andere gelijkstroomapparaten in het nanogrid te integreren. Tijdens een gesprek met de cto en de voorzitter van het USB-IF bleek dat ook de organisatie achter usb, die onder meer power-delivery ondersteunt, dit nanogridconcept steunt. Volgens hen zouden landen als India en China, en andere landen waar het elektriciteitsnetwerk nog niet helemaal dekkend is, de beste kandidaten zijn voor dergelijke nanogrids. Er zou daar minder weerstand zijn van bestaande infrastructuur.

Tot slot

Bijna alle technieken die tijdens het Imec Technology Forum getoond worden, zijn typische wetenschappelijke ontwikkelingen, die bijna altijd minstens drie tot vijf jaar in de toekomst liggen. Sommige technieken laten wellicht nog een stuk langer op zich wachten of worden nooit in de praktijk gebracht. Zo is het natuurlijk goed mogelijk dat over enkele jaren een veel betere techniek wordt ontwikkeld om 5nm-transistors te maken of dat euv toch niet kosteneffectief inzetbaar blijkt te zijn voor massaproductie.

Andere technieken, zoals nanogrids in kantoren en gebouwen, laten misschien wat langer op zich wachten en zijn zelfs beter geschikt voor gebieden waar nog geen gevestigde infrastructuur de uitrol in de weg zit. Dat geldt in mindere mate voor iot-toepassingen, die in de komende jaren naar verwachting grotendeels onzichtbaar ingezet zullen worden, vooral in industriële toepassingen. Die paar smarthome-installaties, daar zit het grote geld niet, maar in duizenden of miljoenen sensors in fabrieken of distributiecentra wel.

Vorderingen op het gebied van gezondheid lijken altijd meer een wensdroom dan werkelijkheid, maar zullen in gespecialiseerde laboratoria steeds meer gemeengoed worden. Het moment dat elke patiënt zijn of haar dna in kaart kan laten brengen en dat op metaniveau via databases kan delen om neurale netwerken mee te voeden, zijn waarschijnlijk nog ver weg. Al is het alleen maar omdat de gezondheidsindustrie traag en log is, en er tal van regels in de weg staan om dergelijke privacygevoelige informatie te delen.

Daarmee lijkt het imec tijdens zijn ITF enerzijds een informatieve vooruitblik op de ontwikkelingen in de halfgeleiderindustrie te geven en anderzijds wellicht wat utopische what-if-scenario's te schetsen van wat er zoal mogelijk is met voldoende rekenkracht, bandbreedte en innovatie.

/i/2001550817.png?f=imagenormal) Een van de opvallendste elementen in haar presentatie was een grafiek met transistorscaling in de komende jaren. Momenteel bevinden we ons in de transitieperiode van 14 naar 10nm, maar op de kaart stonden bekende kleinere nodes als 7, 5 en zelfs 3 en 2nm. De node daarna, gepland voor introductie rond 2025 of 2026, spreekt echter niet meer van nanometers, maar van ångström, een eenheid die normaal gesproken gereserveerd is om individuele atomen te beschrijven. Op de roadmap is sprake van een 14A-node, wat overeenkomt met 1,4nm, aangezien één ångström 0,1nm is.

Een van de opvallendste elementen in haar presentatie was een grafiek met transistorscaling in de komende jaren. Momenteel bevinden we ons in de transitieperiode van 14 naar 10nm, maar op de kaart stonden bekende kleinere nodes als 7, 5 en zelfs 3 en 2nm. De node daarna, gepland voor introductie rond 2025 of 2026, spreekt echter niet meer van nanometers, maar van ångström, een eenheid die normaal gesproken gereserveerd is om individuele atomen te beschrijven. Op de roadmap is sprake van een 14A-node, wat overeenkomt met 1,4nm, aangezien één ångström 0,1nm is.

/i/2001550867.png?f=imagenormal)

/i/2001550865.png?f=imagenormal)

/i/2001550869.png?f=imagenormal)

/i/2001550873.png?f=imagenormal)

/i/2001550875.png?f=imagenormal)

/i/2001550877.png?f=imagemedium)

/i/2001550879.png?f=imagemedium)

/i/2001550887.png?f=imagenormal)

/i/2001550889.png?f=imagenormal)

/i/2001550929.png?f=imagenormal)

/i/2001550943.png?f=imagemedium)

/i/2001550945.png?f=imagemedium)

Een oplossing ligt volgens Energyville, een consortium van onder meer het imec, de universiteit van Leuven en Hasselt, in de integratie van photovoltaics in gebouwen. Doorzichtige zonnepanelen kunnen in ramen, puien en daken geïntegreerd worden. Een tactiek om dat minder opzichtig en tegelijk effectiever te maken, is het gebruik van veel dunne draden in plaats van centrale busbars om de individuele pv-cellen aan elkaar te knopen. Dat lost het kenmerkende modulaire en storende uiterlijk van zonnecellen op, en geeft de panelen een uniforme uitstraling. Die dunne bekabeling zou de productie ook goedkoper en eenvoudiger maken, omdat de interconnects als geweven doek over de modules heen gelegd kunnen worden. Elektronica als power optimizers kunnen in kozijnen worden verwerkt om dankzij korte kabels de rendementen zo hoog mogelijk te maken.

Een oplossing ligt volgens Energyville, een consortium van onder meer het imec, de universiteit van Leuven en Hasselt, in de integratie van photovoltaics in gebouwen. Doorzichtige zonnepanelen kunnen in ramen, puien en daken geïntegreerd worden. Een tactiek om dat minder opzichtig en tegelijk effectiever te maken, is het gebruik van veel dunne draden in plaats van centrale busbars om de individuele pv-cellen aan elkaar te knopen. Dat lost het kenmerkende modulaire en storende uiterlijk van zonnecellen op, en geeft de panelen een uniforme uitstraling. Die dunne bekabeling zou de productie ook goedkoper en eenvoudiger maken, omdat de interconnects als geweven doek over de modules heen gelegd kunnen worden. Elektronica als power optimizers kunnen in kozijnen worden verwerkt om dankzij korte kabels de rendementen zo hoog mogelijk te maken./i/2001550907.png?f=imagenormal)

/i/2001550921.png?f=imagenormal)

:strip_icc():strip_exif()/i/2007287756.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2006208958.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2005704922.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2005286184.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2005184414.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2005169150.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2004698074.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2003043920.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2002874840.jpeg?f=fpa_thumb)

/i/2001566893.png?f=fpa_thumb)

:strip_icc():strip_exif()/i/2001508423.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2001385603.jpeg?f=fpa_thumb)

/i/1383492840.png?f=fpa_thumb)

:strip_exif()/i/2005283572.jpeg?f=fpa)

/i/2004611214.png?f=fpa)

/i/2001435495.png?f=fpa)

/i/1247738571.png?f=fpa)

/i/1240844012.png?f=fpa)

/i/1383492957.png?f=fpa)

/i/1235034622.png?f=fpa)

:strip_exif()/i/1257241493.gif?f=fpa)

/i/1304670251.png?f=fpa)

:strip_exif()/i/1121339114.gif?f=fpa)