Vorige week reisden onze collega's van Materiel.be op uitnodiging van AMD naar Parijs, voor een informatieve bijeenkomst met Tom Sonderman, directeur Automated Precision Manufacturing (APM) bij AMD. Sonderman is verantwoordelijk voor de productielijnen en met name voor het optimaliseren van de productieprocessen van (nieuwe) CPUs, vertrekkend vanaf de eerste prototypes en samples, strevend naar een serieproductie met een hoge opbrengst aan werkende chips (yields). En dit natuurlijk in een zo kort mogelijk tijdbestek om niet meer omzet en marktaandeel mis te lopen dan nodig is. Momenteel wordt gewerkt aan het (volume)productierijp maken van het 90nm-procédé waarop AMD's Opteron en Athlon 64-chips straks gebakken gaan worden en Sonderman wil de pers graag laten weten dat dit voorspoedig verloopt.

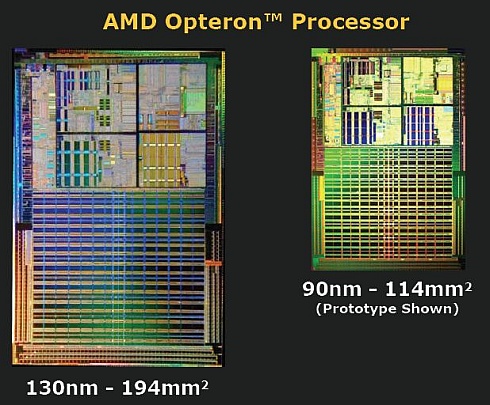

De zogenaamde 'Manufacture Processor Unit Yield Ramp' verloopt niet rampzalig maar vlot, als we Tom Sonderman mogen geloven. Het gaat hier om het opvoeren van het aantal goedgekeurde CPUs per wafer (yields) - vanaf het prototypestadium - tot een dusdanig niveau, dat serieproductie en uitlevering van processors groen licht kunnen krijgen. Exacte getallen worden niet genoemd en het blijft dus giswerk, maar wel kon worden prijsgegeven dat de tijdspanne van deze 'MPU Yield Ramp'-fase voor de Opteron met 66% is ingekort ten opzichte van die indertijd voor de Barton benodigd was. Dit kan een indicatie zijn voor een vlot verlopende invoering van het 90nm-procédé. AMD lag een heel tot een half jaar achter op Intel als het ging om het invoeren van nieuwe, kleinere procédés, maar als het AMD lukt nog deze zomer (derde kwartaal) de eerste 90nm-chips te verzenden, dan is die achterstand teruggebracht tot enkele maanden. Getoond werd een plaatje van een Opteron-prototype op 90nm naast de huidige op 130nm.

De zogenaamde 'Manufacture Processor Unit Yield Ramp' verloopt niet rampzalig maar vlot, als we Tom Sonderman mogen geloven. Het gaat hier om het opvoeren van het aantal goedgekeurde CPUs per wafer (yields) - vanaf het prototypestadium - tot een dusdanig niveau, dat serieproductie en uitlevering van processors groen licht kunnen krijgen. Exacte getallen worden niet genoemd en het blijft dus giswerk, maar wel kon worden prijsgegeven dat de tijdspanne van deze 'MPU Yield Ramp'-fase voor de Opteron met 66% is ingekort ten opzichte van die indertijd voor de Barton benodigd was. Dit kan een indicatie zijn voor een vlot verlopende invoering van het 90nm-procédé. AMD lag een heel tot een half jaar achter op Intel als het ging om het invoeren van nieuwe, kleinere procédés, maar als het AMD lukt nog deze zomer (derde kwartaal) de eerste 90nm-chips te verzenden, dan is die achterstand teruggebracht tot enkele maanden. Getoond werd een plaatje van een Opteron-prototype op 90nm naast de huidige op 130nm.

Andere informatie die Thomas Sonderman meedeelde betrof het succesvolle flashgeheugen, waar AMD het afgelopen kwartaal meer omzet in wist te behalen dan in zijn processors. Flash is dus grotendeels verantwoordelijk voor de zwarte cijfers van AMD in het afgelopen kwartaal. Ook de geplande uitbreiding van Fab 30 met Fab 36 werd aangekaart. In 2006 zou deze 300mm wafers bakkende Fab uit de grond moeten zijn gestampt, met een kostenplaatje van 2,4 miljard dollar. Aanvankelijk is het de bedoeling dat hier 13.000 wafers per maand uit de ovens komen, om later te stijgen naar 20.000 'pizza's di silicone' per maand. Dat zou uiteindelijk bijna een verdubbeling van de chipproductie mogelijk moeten maken. Over de release van het Socket 939-platform kon alleen verteld worden dat er nog geen vaste of officiële datum geprikt was, maar dat die dag niet ver weg was...