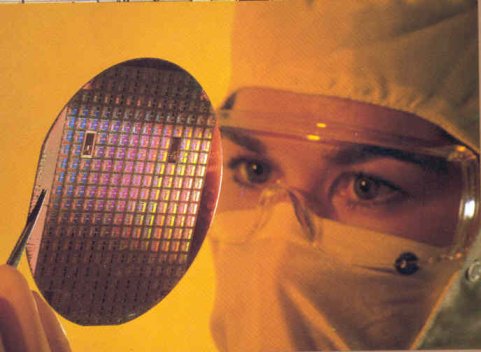

In een bericht op ZDNet is te lezen dat IBM nog steeds problemen heeft met de productie van chips op het 300mm-waferprocédé. De problemen zijn wel wat afgenomen maar de productieresultaten, de zogenaamde 'yields', zijn nog niet geheel naar verwachting. Vanwege deze problemen heeft Apple eerder al commentaar geleverd op IBM vanwege de vertragingen in de levering van de Xserve G5-machines, die de IBM PowerPC-processor onder de motorkap hebben. Toen de G5 in juni vorig jaar werd geïntroduceerd sprak Apple de verwachting uit dat deze binnen een jaar op 3GHz zou draaien. De vraag is echter met de aanhoudende problemen bij IBM, of die verwachting waargemaakt kan worden.

Door het voortdurend verkleinen van de transistors op een chip lopen de chipfabrikanten waaronder IBM nu steeds vaker tegen praktische problemen aan, die niet met de huidige technologie op te lossen zijn. Bernie Meyerson van IBM zegt in het artikel dat het een flinke uitdaging zal worden om nieuwe technieken en procédé's te ontwikkelen om toch de prestaties van chips te kunnen verhogen, en dat het onderzoek daarvoor nog wel vijf tot tien jaar kan gaan duren. Meyerson zegt echter wel, dat IBM al hard bezig is met dergelijke technologieën, die op dit moment bekend staan onder de namen strained silicon, high-k dielectrics en hybrid-orientation.