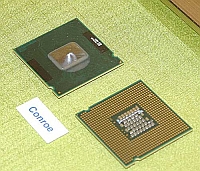

Interne memo's en roadmaps van Intel zouden bevestigen dat Intels volgende processorgeneratie ondersteuning biedt aan SSE4-instructies, naast al langer bestaande instructiesets waaronder mmx, SSE, SSE2, SSE3, en x86-64. De nieuwe lichting chips gaan momenteel nog door het r&d-leven onder de schuilnamen Conroe, Merom en Woodcrest, en zijn respectievelijk bedoeld voor desktops, notebooks en servers. De nieuwe instructies zijn onder andere bedoeld om het rekenen met absolute getallen te versnellen en de mogelijkheden van het werken met algoritmes uit te breiden. Dat laatste kan op een manier geschieden waarmee minder instructies en registers nodig zijn en er verschillende optimalisaties mogelijk worden. De nieuwe instructieset, waarover we al eerder schreven, maakt onderdeel uit van wat Intel eerder globaal omschreef als 'Significant Video Enhancements' van de volgende generatie processors.

Andere onderdelen van de 'SVE-features' zijn Clear Video Technology (CVT), een soort tegenhanger van ATi's Avivo, en ondersteuning voor UDI (unified display interface), een opvolger voor computerbeeldscherm-interfaces VGA, DVI en HDMI. Eerdere documenten van Intel omschreven CVT als een technologie 'supporting advanced decoding, post-processing capabilities and enhanced 3d.' Deze laatste features zullen wellicht in de i965-chipset zijn ondergebracht, en niet per se in de cpu. Conroe, Merom en/of Woodcrest zullen naar verwachting op het Intel Developer Forum (van 7 tot 9 maart) hun opwachting maken. De eerste chips van deze nieuwe generatie worden nog dit jaar verwacht.

Andere onderdelen van de 'SVE-features' zijn Clear Video Technology (CVT), een soort tegenhanger van ATi's Avivo, en ondersteuning voor UDI (unified display interface), een opvolger voor computerbeeldscherm-interfaces VGA, DVI en HDMI. Eerdere documenten van Intel omschreven CVT als een technologie 'supporting advanced decoding, post-processing capabilities and enhanced 3d.' Deze laatste features zullen wellicht in de i965-chipset zijn ondergebracht, en niet per se in de cpu. Conroe, Merom en/of Woodcrest zullen naar verwachting op het Intel Developer Forum (van 7 tot 9 maart) hun opwachting maken. De eerste chips van deze nieuwe generatie worden nog dit jaar verwacht.