Intel heeft aangekondigd dat zijn 45nm-processors voorzien zullen worden van ongeveer vijftig nieuwe instructies, die samen SSE4 zullen worden genoemd. De functies kunnen grofweg verdeeld worden in drie groepen: het eerste en overgrote deel is bedoeld om multimedia te versnellen, waaronder spellen, video en 2d/3d-rendering. Om dit soort toepassingen te helpen geeft de instructieset ontwikkelaars en compilers meer gereedschap om met vectoren te werken. Ondanks het feit dat er op dit moment al 259 instructies bestaan in SSE1 tot en met SSE3, hoefde men zich verrassend genoeg toch niet in vreemde bochten te wringen om nog nieuwe features te verzinnen: vrij voor de hand liggende operaties als het opzoeken van het laagste of hoogste getal, afronden, vergelijken en het uitrekenen van een Dot Product (standaardgereedschap voor alles wat zich met 3d bezighoudt) zitten er kennelijk nog niet in. Andere nieuwe instructies verbeteren de prestaties door de samenwerking tussen normale code en vectorcode te versoepelen, bijvoorbeeld door snelle conversie tussen verschillende datatypes.

Het tweede belangrijke deel van SSE4 zijn instructies die het doorzoeken en vergelijken van tekst versnellen. Intel verwacht dat deze erg nuttig zullen zijn voor zaken als virusscanners, compressie, databases en compilers. Ten derde zullen er nog een paar applicatiespecifieke functies worden toegevoegd: een hardwarematige implementatie van het CRC-algoritme (dat bijvoorbeeld gebruikt wordt om te controleren of bestanden intact zijn) en een zogeheten 'pop counter' die telt hoe vaak de binaire 1 voorkomt in een getal. Laatstgenoemde is nuttig voor patroonherkenning en schijnt naast de officiële doelstellingen als handschriftsoftware en gen-

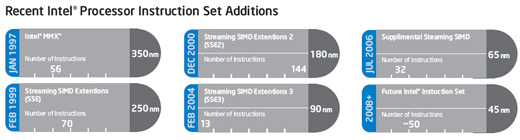

Overigens is de naamgeving 'SSE4' voor sommige mensen wellicht verwarrend, want eerder werd her en der aangenomen dat de nieuwe instructies in de Core 2-processor zo (zouden gaan) heten. De 32 nieuwe instructies in Woodcrest, Conroe en Merom schijnt men echter niet spannend genoeg te vinden om een nieuw versienummer te rechtvaardigen, en deze zijn nu dan ook officieel omgedoopt tot 'Supplemental SSE3'.