Op PC Watch Japan is een hoop nieuwe informatie verschenen over Montecito, een nieuwe versie van de Itanium-processor die Intel in de tweede helft van 2005 zal introduceren. Deze specificaties zijn oorspronkelijk afkomstig van HotChips 16, een conferentie waarop Intel eind augustus een presentatie over de chip heeft gegeven. Het meest opvallende nieuwe feit is dat de TDP van de bijna twee miljard transistors tellende chip op 100 Watt is vastgesteld, 30 Watt láger dan dat van de huidige Madison-serie. Dit terwijl de kloksnelheid van de Itanium niet alleen verhoogd wordt van 2,0 naar 2,5GHz, maar er ook nog eens een hele tweede core aan de chip wordt toegevoegd. De overstap van 130nm- naar 90nm-productie werpt voor Itanium dus duidelijk meer vruchten af dan voor de Pentium 4.

De basis van Montecito is een derdegeneratie Itanium-core. Qua executie-eenheden is deze identiek aan de tweede generatie, maar de cachestructuur is drastisch verbeterd en er zijn enkele belangrijke nieuwe features toegevoegd, deels voor extra prestaties en deels voor meer betrouwbaarheid. De meest opvallende verandering qua cache is het splitsen van de L2-cache in aparte stukken voor data (256KB) en instructies (1MB). De meeste moderne processors maken dit onderscheid wel op L1, maar hebben op L2 een gemixt (unified) cache zitten. Het splitsen maakt het makkelijker om lage latencies te halen en biedt bovendien een performancevoordeel: data kan code niet meer het cache uit duwen en andersom.

Verder is de L1-instructiecache vergroot van 16 naar 18KB. De reden hiervoor is niet geheel duidelijk, maar mogelijk gaat het om extra ruimte voor de branch predictor of Coarse-grained MultiThreading. CMT is de techniek waarmee vier threads op de dual-core chip kunnen draaien. Niet geheel tegelijkertijd zoals bij SMT (HyperThreading) gebeurt, maar meer om de beurt; terwijl de ene thread op data uit het geheugen wacht kunnen bijvoorbeeld instructies voor de andere thread uitgevoerd worden. CMT is dus wel wat minder geavanceerd dan SMT, maar blijft nog steeds vele malen sneller dan het uitvoeren van dezelfde truc via software. Verder is er een L3-cache van 12MB en worden er nog drie nieuwe technieken geïntroduceerd. Foxton zorgt voor het dynamisch over- en onderklokken van de chip, voor betere prestaties en meer zuinigheid. Pelston beschermt de processor tegen cachefouten en Silvervale verbetert de ondersteuning voor virtual machines.

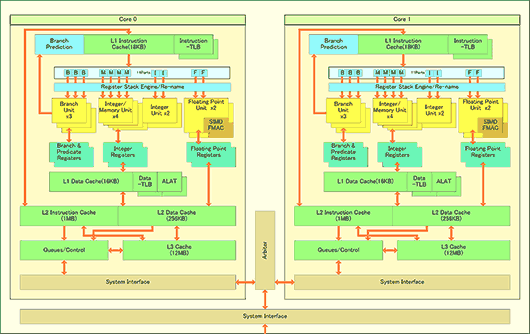

Het schema toont een tweetal van de hierboven beschreven cores die aan elkaar en de bus gekoppeld zijn middels een arbiter: de architectuur van de Montecito. Hoe het aanbod van de goedkopere Millington-chips eruit komt te zien is nog niet duidelijk, maar het is niet meer dan logisch dat er versies met slechts één core en een kleiner L3-cache geleverd zullen worden. In het schema valt overigens op dat er geen x86-eenheid meer wordt getoond. De huidige Itaniums hebben stuk voor stuk een hele berg extra transistors om backwards compatible te blijven, maar IA-32EL heeft dat eigenlijk overbodig gemaakt. Het is echter niet zeker of de x86-hardware écht gedumpt is, het zou namelijk ook gewoon uit de presentatie gelaten kunnen zijn om het diagram niet ingewikkelder te maken dan het al is.