AnandTech heeft gisteren al een deel van de informatie behandeld, maar bij Aikiba is nu een uitgebreider artikel verschenen over de Prescott-details die op IDF zijn vrijgegeven, en dan met name over P1262. De die-hard tweaker herkent dit codenummer als de officiële naam voor het 90nm-procédé. Naast verbeteringen aan de architectuur wordt namelijk ook de productie van de chip flink veranderd. Niet alleen worden de transistors twee keer zo klein (van 130 bij 70nm naar 90 bij 50nm) maar ook zal het bedrijf gebruik gaan maken van strained silicon en SiGe-technologie om warmte te verminderen en yields te verhogen.

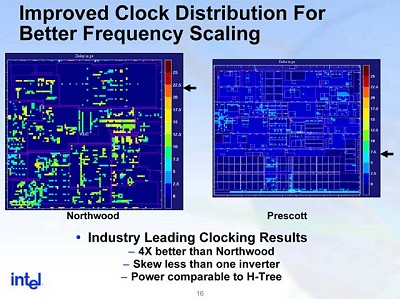

Daarnaast is de manier waarop Prescott ontworpen sterk verbeterd. Een complexe chip als deze (ongeveer 100 miljoen transistors) wordt natuurlijk niet micron voor micron opgebouwd door mensenhanden, maar door complexe algoritmes die in een flinke cluster draaien gegenereerd aan de hand van een beschrijving op hoger niveau. De beste analogie is die van software: de sourcecode wordt door een compiler omgezet naar een werkend programma. De "chipcompiler" is sinds de release van Northwood flink verbeterd. Door iedere transistor en interconnect zorgvuldiger te plaatsen kunnen problemen worden voorkomen die ontstaan wanneer signalen met frequenties van meerdere gigahertzen langs elkaar en door elkaar heen lopen. Zo is het mogelijk dat twee signalen elkaar opheffen, of dat het een signaal door verspringende electronen een 'vals' signaal veroorzaakt in een circuit waar het toevallig bij in de buurt komt. Hoe minder de signalen elkaar in de weg zetten, hoe hoger een chip geklokt kan worden zonder onstabiel te worden. Hieronder zie je het resultaat:

:strip_exif()/i/1043707449.gif?f=fpa)