Ars Technica heeft bijna een jaar na de introductie van de Pentium M-processor, deze aan een nader onderzoek onderworpen. Hierbij wordt er ingegaan op de technische aspecten van de processor en de microarchitectuur van de chip. De Pentium M is gebaseerd op de P6-architectuur van Intel. Op deze architectuur waren eerder al de 32-bit desktopprocessors Pentium Pro en Pentium III gefundeerd, maar in de Pentium M komen ook kneepjes uit de Pentium 4-architectuur voor. Verder zijn er een aantal vernieuwingen in te vinden, die niet in andere processors zijn terug te vinden. Hoewel Intel niet al te loslippig is over de Pentium M, zijn er hier en daar wel wat interessante zaken te melden, vandaar de blik door het vergrootglas van Ars Technica.

![]() Pipeline en execution core

Pipeline en execution core

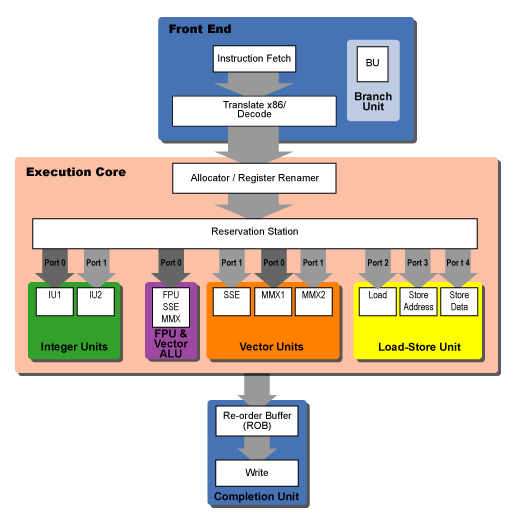

Allereerst wordt er gekeken naar de pipeline en de execution core. Hier zijn de kleinste verschillen tussen de Pentium III-processor en de Pentium M-processor waar te nemen. Het onderstaande diagram behandelt de P6-architectuur op basis van de Pentium III, waarbij de verschillen met de Pentium M voornamelijk op het gebied van het reservation station zijn. Waar de Pentium III maximaal vijf micro-operations (uops) per cyclus kan verwerken, is dit bij de Pentium M mogelijk opgevoerd tot twintig. Verder zijn het aantal ingangen in de reorder buffer opgewaardeerd naar veertig. In vergelijking met de Pentium 4 zijn er weinig verschillen in de prestaties op het gebied van integer- en floating point-berekeningen, al blijft de aanvoerder - de PowerPC 970 - ver buiten bereik.

Het vermoeden bestaat echter dat dit diagram de waarheid omtrent de Pentium M niet geheel eer aan doet. Het is zeer goed mogelijk dat Intel een aantal aanpassingen heeft uitgevoerd met betrekking tot de FPU en vectorberekeningen. Uiteraard kan de Pentium M klok-voor-klok uitstekend mee met de Pentium 4 - gebaseerd op eerdere vergelijkingen tussen Pentium III en Pentium 4 - maar doordat de pipeline van de processors dusdanig verschillen, is een eerlijke vergelijking klok-voor-klok niet mogelijk. Ook het verschil in stroomverbruik is dusdanig, wat grotendeels te verklaren is doordat de Pentium 4 niet specifiek bedoeld is voor mobiel gebruik.

De pipeline van de Pentium M is een stukje langer dan die van de Pentium III, maar wel korter dan die van de Pentium 4. Deze verlenging heeft waarschijnlijk te maken met het feit dat zo de kloksnelheid verhoogd kan worden om meer uops per cyclus te kunnen verwerken. Dit is echter niet de voornaamste reden waarom de Pentium M zo goed presteert; branch prediction speelt namelijk een nog grotere rol. Dankzij de verbetering hiervan is de efficiency van de processor een flink stuk omhoog gegaan. Het valt weliswaar in het niet met - alweer - de PowerPC 970, maar het is stukken beter dan zowel de Pentium III als 4. De Pentium M gebruikt dezelfde branche predictor als van de Pentium 4, maar dan met twee toevoegingen. De Loop Detector en de indirecte branch detector zijn twee gespecialiseerde branch detectors en deze werken gezamenlijk met de originele branch detector.

![]() Branch prediction

Branch prediction

Wanneer er wordt gekeken naar de branch-prediction van Intel zien we dat er gebruik gemaakt wordt van een dynamische versie hiervan. Hierdoor ontstaan er geen problemen met een branch zonder lus, daar namelijk de geschiedenis bijgehouden wordt van de voorspellingsresultaten. Dit levert juistere voorspellingen op, alleen is er een manco. De juistheid van deze voorspellingen neemt toe naarmate de geschiedenis beter wordt bijgehouden, dat wil zeggen over een langere periode. Bij de Pentium 4 wordt er gebruikgemaakt van een 4096-entry branch history table (BHT) in combinatie met een zeer accuraat voorspellingsalgoritme. De BHT is daarnaast ook nog redelijk groot, alleen is het niet groot genoeg om de volledige geschiedenis van de voorspellingen bij te houden. Zeker wanneer er in de lus flink wat herhalingen moeten worden uitgevoerd, raakt de 4K-buffer van de BHT snel vol. Deze 4096-buffer wordt trouwens voor elke gekozen branch opgesteld.

De Loop Detector - hoe kan het ook anders - analyseert de branch op eventuele lussen in een bepaalde aftakking. Wanneer zo'n branch is ontdekt, worden er resources vrijgemaakt om deze in zijn geheel uit te voeren en te voorspellen. Een belangrijke toevoeging dus op de Pentium 4-BHT. De indirecte branch predictor is er voor om een aftakking uit te voeren wanneer er meerdere oplossingsmogelijkheden zijn, bijvoorbeeld een eindspel in het schaken. Aangezien er meerdere oplossingen zijn, is het niet makkelijk om te voorspellen welke aftakking er wordt genomen door de software. Ondanks dit alles is een accuratessegraad van 75 procent haalbaar, waarbij directe branch predictors 97 procent halen.

De werking van de indirect branch predictor lijkt veel op de BHT, maar er wordt andere informatie opgeslagen. Dit is namelijk de favoriete keuze van de branch en onder welke condities deze keuze wordt gemaakt. Dankzij deze verbeteringen en toevoegingen is de accuratessegraad van de Pentium M twintig procent omhoog gegaan, wat een daadwerkelijke performancewinst betekent van zeven procent. Dit hangt uiteraard af van welke software er wordt gebruikt, maar naast de performancewinst is er ook een efficiency in het stroomverbruik gerealiseerd. Dit komt doordat er minder energie verspild wordt met verkeerde voorspellingen.

![]() Micro-op fusion en stack execution unit

Micro-op fusion en stack execution unit

Een van de meest fascinerende vernieuwingen van de Pentium M, is de wijze waarop deze de uops behandeld. Dit komt qua werking dicht in de buurt bij hoe de PowerPC 970 omgaat met het groeperen van instructies. Uops worden gedistilleerd uit de instructiecode die naar de processor toe worden gezonden. De processor kan de code echter niet op deze manier verwerken, vandaar dat de instructiecode wordt opgedeeld in nog kleinere stukjes die wel te behappen zijn door de execution core van de P6, de zogenaamde uops. Om al deze uops uit elkaar te houden en later weer bij elkaar te voegen komen de reorder buffer en het reservation station om de hoek kijken. Door de vergroting van het aantal ingangen in de reorder buffer en van de verwerkingsnelheid van het reservation station is het nu mogelijk om de honger van de verbeterde P6-execution core tevreden te stellen. Het punt is echter wel, hoe meer gegevens, des te meer transistors er worden gebruikt en des te meer stroom benodigd is. Laat dat nou net niet de bedoeling zijn van de Pentium M.

Dit is opgelost door bepaalde uops met elkaar te laten fuseren. Deze fusies vinden plaats tussen gelijke en gerelateerde soorten uops en worden derhalve toegewezen tot één reorder buffer- en reservation station-invoer. Dit heeft geen invloed op de berekening van de uops - deze worden nog altijd apart berekend - maar de gefuseerde uops worden wel als groep behandeld, wat dus scheelt in het aantal toegewezen transistors. Omdat de Pentium M niet van begin af aan is ontworpen, maar op basis van de P6-core, zijn er wel een aantal beperkingen waarmee rekening gehouden moest worden. Zo zou het reservation station van de P6 helemaal opnieuw ontworpen moeten worden, wat niet de bedoeling was.

Vandaar dat de micro-op fusion beperkt blijft tot een tweetal specifieke instructietypen: de laad- en de opslaginstructie. Of er nog meerdere instructietypen worden gefuseerd is niet duidelijk. In ieder geval de reden waarom de laad- en opslaginstructie wel worden gefuseerd is de volgende: volgens Intel wordt er namelijk een performanceverbetering van vijf procent voor integer-code en negen procent voor floating point-code behaald, dankzij micro-op fusie. Verder zorgt de laadinstructie voor het grootste deel van de integer-code perfomancewinst. Terwijl de twee instructietypen ongeveer evenveel bijdragen aan de verbeteringen omtrent de floating point-codeberekeningen.

De stack execution unit elimineert de noodzaak voor het gebruik van een speciale uop, die gebruikt wordt door de Pentium III- en Pentium 4-core. Deze uop past de stack pointer register - ESP - aan zodat de toegewezen waarden kunnen worden opgeteld of verminderd. Door toezicht te houden op de stroom aan instructies uit de decoder kan de stack execution unit de taken van de specifieke uop overnemen. Hierdoor ontstaan er een aantal voordelen, uiteraard zijn er minder uops nodig, wat er weer voor zorgt dat er minder transistors per taak in beslag worden genomen en dus uiteindelijk een stroombesparing oplevert. Verder, doordat er minder ruimte door de integer execution units in beslag worden genomen voor het aanpassen van de ESP, kunnen deze worden toegewezen aan andere berekeningen, wat weer tot een snelheidsverbetering leidt.

![]() Conclusie

Conclusie

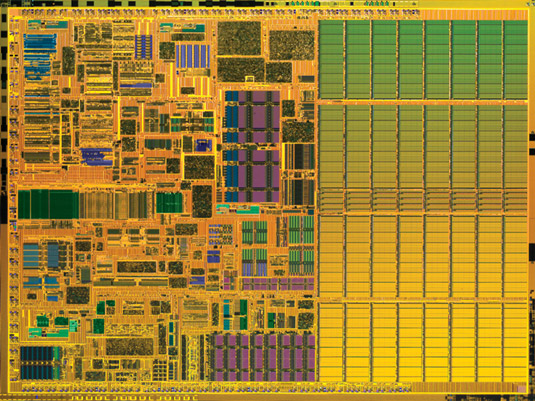

Door het sterke punt van de Pentium 4 te combineren met de voordelen van de P6-core heeft Intel een uitstekende processor kunnen ontwerpen en neerzetten. De Pentium M is zeker niet alleen interessant voor de mobiele markt, ook in servers kan deze processor makkelijk zijn mannetje staan. Wanneer hieraan ook nog IA-32e-ondersteuning gehangen gaat worden kan de Pentium M zelfs een voorname rol op de desktopmarkt gaan spelen. Dit ondermeer dankzij de 1MB L2-cache en de 64KB L1-cache. De laatste is hierbij twee keer zo groot als waarmee de Pentium 4 het moet doen. Het is ook nog mogelijk dat de Pentium M in de toekomst wordt ingezet in een groep, waarbij meerdere zuinige processors worden aangestuurd door multi-threaded software. Een andere optie die nog wordt voorgedragen is dat de Pentium M als opvolger van de Prescott kan gaan dienen, wanneer de laatste niet het resultaat bereikt dat Intel ervan verwacht. Een wilde gedachte weliswaar, maar de toekomst zal het leren.

:strip_exif()/i/1093383592.gif?f=fpa)