IBM heeft een presentatie gegeven over zijn nieuwe mainframeprocessor, de z6. De chip is losjes gebaseerd op de architectuur van de Power6, maar heeft meer dan genoeg unieke features om van een nieuw ontwerp te kunnen spreken.

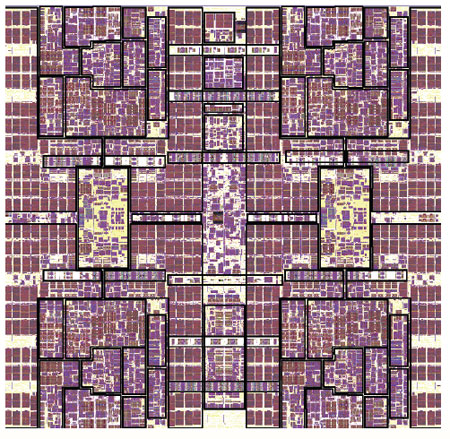

De z6 is een 65nm quadcoreprocessor van 434mm² met 991 miljoen transistors aan boord. De chip werkt op Socket 8765, draait op snelheden boven de 4,0GHz en biedt een totale bandbreedte van 182GB/s uit onder meer vier geheugencontrollers.

De z6 is een 65nm quadcoreprocessor van 434mm² met 991 miljoen transistors aan boord. De chip werkt op Socket 8765, draait op snelheden boven de 4,0GHz en biedt een totale bandbreedte van 182GB/s uit onder meer vier geheugencontrollers.

Iedere core heeft 192KB L1-cache en 3MB L2-cache direct geïntegreerd, wat verder wordt aangevuld met een gedeeld extern L3-cache van 24MB, dat eventueel naar 48MB vergroot kan worden. De pipeline en bepaalde rekeneenheden van de z6 zijn op die van de Power6 gebaseerd, maar er zijn ook grote verschillen tussen de twee; zo hebben ze om te beginnen al een heel andere instructieset.

Nieuwe features in de z6 zijn onder andere de optie om hardwarematig om te gaan met decimale floating point-

De betrouwbaarheid van de z6 gaat ook nog een stap verder dan die van de Power6. Zo controleert de chip op meer dan twintigduizend plaatsen of er geen fouten zijn opgetreden bij het opslaan, versturen of verwerken van data. Vrijwel iedere fout kan opgelost worden: de core zal eerst proberen zijn eigen state te herstellen en de actie zelf opnieuw uit te voeren, maar als dat niet lukt is het ook nog mogelijk om de taak door een andere chip over te laten nemen, allemaal zonder dat de software er iets van hoeft te merken.

Over het stroomverbruik van dit monster is niets bekendgemaakt, maar het is geen geheim dat zelfs mainframes met een bescheiden aantal processors aan boord al enkele duizenden watts verorberen. Het mag dus duidelijk zijn dat deze chips hun prestatie/

/i/1279796738.png?f=fpa)

:strip_exif()/i/1194891781.gif?f=fpa)