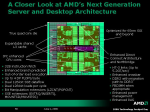

AMD heeft tijdens de AMD Technology Analyst Day de volgende generatie processors in detail belicht. Opvallend was dat AMD de nieuwe generatie niet bij naam noemde, maar alleen sprak van een nieuwe architectuur. De gepresenteerde microarchitectuur toont echter grote overeenkomsten met het K8L-ontwerp dat onlangs werd besproken. De nieuwe architectuur bestaat uit vier cores en elke core beschikt over 64KB L1-cachegeheugen (32KB data- en 32KB instructiecachegeheugen) en 512KB L2-cachegeheugen. Opvallend is dat AMD de grootte van het L1-cachegeheugen door tweeën heeft gedeeld, want de huidige K8 heeft 64KB L1-data- en 64KB L1-instructiecachegeheugen. Volgens AMD zou dit echter niet veel invloed hebben op de prestaties, daar alle vier de cores een L3-cachegeheugen delen dat in eerste instantie 2MB groot is. Processors met meer L3-cachegeheugen zouden ook op de roadmap staan.

De architectuur zou volgens AMD een modulair ontwerp zijn. Dat wil zeggen dat elk onderdeel, van L3-cachegeheugen tot rekeneenheden, apart zijn ontworpen en getest om later samengevoegd te worden tot een processor. Dit is echter niks nieuws onder de zon, daar elke moderne chip tegenwoordig op deze manier wordt ontworpen. AMD claimt echter dat dit modulaire ontwerpen nog verder is doorgevoerd door onder andere de interfaces van alle blokken beter te definiëren. AMD liet echter niets los over de reden hierachter. Waarschijnlijk maakt een modulair ontwerp het makkelijker om bepaalde onderdelen later te wijzigen zonder dat dit invloed heeft op andere onderdelen. Ook opent het de mogelijkheid om makkelijker een onderdeel toe te voegen als dit nodig is. Een andere mogelijkheid is dat dit niets anders is dan voorbereidend werk om omgekeerde HyperThreading mogelijk te maken: het uitvoeren van een thread op meerdere cores.

De architectuur zou volgens AMD een modulair ontwerp zijn. Dat wil zeggen dat elk onderdeel, van L3-cachegeheugen tot rekeneenheden, apart zijn ontworpen en getest om later samengevoegd te worden tot een processor. Dit is echter niks nieuws onder de zon, daar elke moderne chip tegenwoordig op deze manier wordt ontworpen. AMD claimt echter dat dit modulaire ontwerpen nog verder is doorgevoerd door onder andere de interfaces van alle blokken beter te definiëren. AMD liet echter niets los over de reden hierachter. Waarschijnlijk maakt een modulair ontwerp het makkelijker om bepaalde onderdelen later te wijzigen zonder dat dit invloed heeft op andere onderdelen. Ook opent het de mogelijkheid om makkelijker een onderdeel toe te voegen als dit nodig is. Een andere mogelijkheid is dat dit niets anders is dan voorbereidend werk om omgekeerde HyperThreading mogelijk te maken: het uitvoeren van een thread op meerdere cores.

Het was al bekend dat de vier cores en de 'northbridge' van de K8L in tegenstelling tot de K8 allemaal op een andere spanning en klok kunnen werken. Cores die niet gebruikt worden, kunnen dus op een lagere klok en/of lager voltage werken of zelfs uitgeschakeld worden. Dit systeem om energie te besparen als de processor niet veel werk hoeft uit te voeren heeft ondertussen van AMD ook een naam gekregen: Dynamic Independent Core Engagement (DICE).

Het was al bekend dat de vier cores en de 'northbridge' van de K8L in tegenstelling tot de K8 allemaal op een andere spanning en klok kunnen werken. Cores die niet gebruikt worden, kunnen dus op een lagere klok en/of lager voltage werken of zelfs uitgeschakeld worden. Dit systeem om energie te besparen als de processor niet veel werk hoeft uit te voeren heeft ondertussen van AMD ook een naam gekregen: Dynamic Independent Core Engagement (DICE).

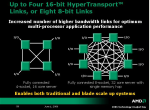

De nieuwe HyperTransport 3.0-bus waarmee de volgende generatie AMD-processors zal zijn uitgerust, zal zijn werk doen op 2,6GHz en 16bits breed zijn, goed voor een bandbreedte van 5,2GB/s. Ter vergelijking: de huidige HyperTransport-bus heeft een maximale frequentie van 1GHz en is ook 16bits breed, goed voor een bandbreedte van 2GB/s. Elke processor krijgt vier van deze bussen. Drie hiervan zijn bedoeld voor de communicatie met andere processors in een multiprocessorsysteem. De vierde kan worden gebruikt voor de chipset om I/O mogelijk te maken. Doordat er drie HT-bussen op de processor zitten, kan er een multiprocessorsysteem gebouwd worden met vier processors die allen een directe link hebben met het cache en het geheugen van een andere processor. Het grote voordeel hiervan is dat de latentie om iets op te zoeken in het geheugen waarover een andere processor beschikt laag gehouden kan worden. De 16-bits HT-links kunnen ook opgesplitst worden in twee 8-bits HT-links, waardoor hetzelfde geintje is uit te halen met acht processors. Gezien de hogere bandbreedte zou dit in theorie niet zoveel mogen uitmaken voor de snelheid.

De nieuwe HyperTransport 3.0-bus waarmee de volgende generatie AMD-processors zal zijn uitgerust, zal zijn werk doen op 2,6GHz en 16bits breed zijn, goed voor een bandbreedte van 5,2GB/s. Ter vergelijking: de huidige HyperTransport-bus heeft een maximale frequentie van 1GHz en is ook 16bits breed, goed voor een bandbreedte van 2GB/s. Elke processor krijgt vier van deze bussen. Drie hiervan zijn bedoeld voor de communicatie met andere processors in een multiprocessorsysteem. De vierde kan worden gebruikt voor de chipset om I/O mogelijk te maken. Doordat er drie HT-bussen op de processor zitten, kan er een multiprocessorsysteem gebouwd worden met vier processors die allen een directe link hebben met het cache en het geheugen van een andere processor. Het grote voordeel hiervan is dat de latentie om iets op te zoeken in het geheugen waarover een andere processor beschikt laag gehouden kan worden. De 16-bits HT-links kunnen ook opgesplitst worden in twee 8-bits HT-links, waardoor hetzelfde geintje is uit te halen met acht processors. Gezien de hogere bandbreedte zou dit in theorie niet zoveel mogen uitmaken voor de snelheid.

Update: Volgens Real World Technologies heeft AMD niet in het L1-cache gesneden. Zowel het instructie- als het datacache zouden 64KB groot zijn. Dit zou bevestigd zijn door een architect bij AMD. Daarnaast bevestigt de afbeelding van de core ook dit vermoeden. Het artikel van DailyTech waarop dit nieuwsbericht is gebaseerd bevat dan ook waarschijnlijk een fout.