EaS wees ons op een diepgaand artikel dat door Hans de Vries is geschreven voor de site Chip Architect. Het artikel begint met de opsomming van maar liefst 16 patenten die rechtstreeks op de K8 architectuur betrekking hebben, die voor het eerst zal verschijnen in de Hammer processors en uiteindelijk de huidige K7 architectuur, bekend van Athlon en Duron, moet gaan opvolgen. De K8 chips zullen 64 bits processors worden die kunnen concurreren met de Itanium van Intel, maar de Hammer blijft in tegenstelling tot de Itanium zonder emulatie compatible met de huidige software.

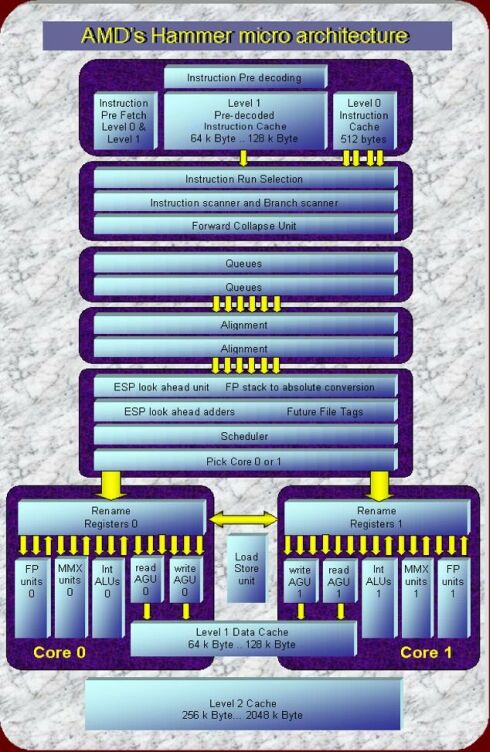

Wat het meest opvalt aan SledgeHammer, de eerste K8 voor servers, zijn de twee CPU-cores waaruit de chip bestaat. Men kan bijna spreken over een dual processor systeem op een chip, maar dat is niet het geval. De SledgeHammer is net zoals de huidige x86 processors een single-threaded processor. Met andere woorden, hij kan maar één instructiestroom tegelijkertijd uitvoeren. Door enkele gepatenteerde mechanismen om de instructiestroom over de twee CPU-cores te verdelen, kan men echter wel een hoge graad van parallellisme bereiken. Daarnaast heeft elke core zijn eigen registerset, wat betekent dat het draaien van twee threads tegelijkertijd in feite mogelijk zou moeten zijn, hoewel hier niks over staat in de patenten. Uiteraard is een nieuwe processor niets zonder de chipset die erbij hoort en daar schrijft Hans de Vries het volgende over:

A number of ClawHammer chipsets have now been placed on the roadmaps. These chipsets use Hyper Transport to communicate with ClawHammer at a presumable speed of 800 MHz and a total bandwidth of 6.4 Giga Byte/s. Three times that of the current 266 MHz EV6 bus. Hyper Transport is said to scale to 1.6 Giga Hertz and 12.8 Giga Byte/s. The Memory Controller is still integrated on the Chipsets with support for 266 and 333 MHz DDR SDRAM. One should hope that these chipsets support 128 bit busses to memory to take advantage of the higher bandwidth.

|