Inleiding: wat is Imec?

Inleiding: wat is Imec?

Het zal bij veel tweakers inmiddels bekend zijn dat Intel jaarlijks zijn Developer Forum, kortweg IDF, organiseert. Daarbij worden niet alleen fabrikanten en ontwikkelaars, maar ook de pers uitgenodigd om de stand van zaken te aanschouwen. Welke technische ontwikkelingen en producten mogen we in de komende jaren uit het blauwe kamp verwachten? Tweakers tijgt daarom jaarlijks een week naar San Francisco om op de hoogte te blijven van de ontwikkelingen.

Het instituut beschikt over een scala aan laboratoria en een eigen 'fab'

Veel dichter bij huis wordt echter ook volop onderzoek gedaan naar toekomstige technieken. In het Belgische Leuven ligt de Imec-campus, een onderzoeksinstituut dat in 1984 door de Vlaamse overheid werd opgericht. Het onderzoekscentrum werkt niet alleen met diverse bedrijven, maar ook met tal van universiteiten samen aan onderzoek naar nieuwe technologie voor elektronica. Het instituut beschikt daartoe onder meer over een scala aan laboratoria en een eigen 'fab', een cleanroom met faciliteiten voor chipproductie.

In zijn bijna dertigjarige bestaan is Imec uitgegroeid tot een gerenommeerd onderzoeksinstituut, waar zo'n tweeduizend werknemers werken. Het instituut heeft rond de zeshonderd samenwerkingsverbanden, onder andere met ongeveer tweehonderd universiteiten.

Jaarlijks organiseert Imec zijn eigen Imec Technology Forum, een naam waarvan de afkorting waarschijnlijk niet toevallig aan Intels event doet denken. Tijdens dit ITF toonde Imec tal van ontwikkelingen, waarvan we een aantal de revue laten passeren. Zo kijken we naar lithografische chipfabricage tot 5nm en welke technieken nodig zijn om transistors kleiner dan 5nm te maken. Ook 3d-technieken voor chips en flexibele elektronica komen aan bod. Ten slotte kijken we naar een zeer direct toepassingsgebied voor nieuwe technologie: de gezondheidszorg.

/i/1383495458.jpeg?f=imagenormal)

De grenzen van lithografie

Moore's Law wordt al jaren als onhaalbaar en aan het eind van zijn toepasbaarheid bestempeld. Desondanks lijkt de observatie van Gordon Moore, een van de grondleggers van Intel, dat de hoeveelheid transistors in een chip elke twee jaar verdubbelt, nog steeds op te gaan. Jaar in jaar uit worden transistors kleiner, neemt hun snelheid toe en worden ze per stuk goedkoper. Toch hebben de critici een punt; de wet is helemaal geen wet, maar een verschijnsel dat zich tot dusver in de praktijk voordeed. Naarmate transistors echter kleiner worden, lijken de grenzen van hun afmetingen langzaam in zicht te komen.

Een lastig punt zijn de metalen connectors om de transistors aan te sturen

Aangezien de ontwikkeling van een procedé jaren duurt, mag het geen verrassing zijn dat nu al volop wordt gewerkt aan zogeheten nodes, stadia in de technologie, met afmetingen ver onder de huidige. Waar de meest geavanceerde procedé's nu 22nm hanteren, wordt al gewerkt aan 14nm, 10nm en nog kleinere nodes. Uiteraard is daarvoor een enorme hoeveelheid research & development nodig; de complexiteit van de producten neemt gigantisch toe naarmate ze kleiner worden. Ook de productie en vooral de apparatuur die nodig is om ze te maken worden complexer en duurder, omdat steeds grotere precisie nodig is. Dat verklaart ook waarom achtereenvolgende chipgeneraties nauwelijks goedkoper worden.

/i/1383495891.png?f=imagenormal)

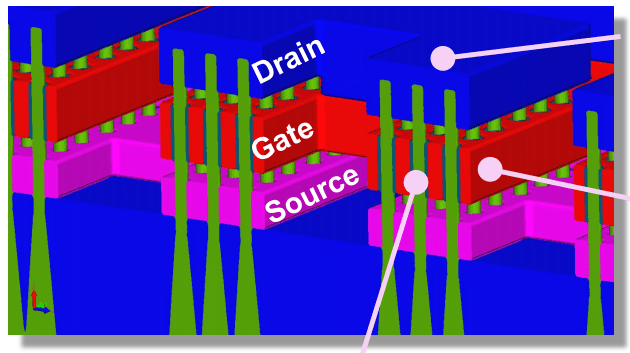

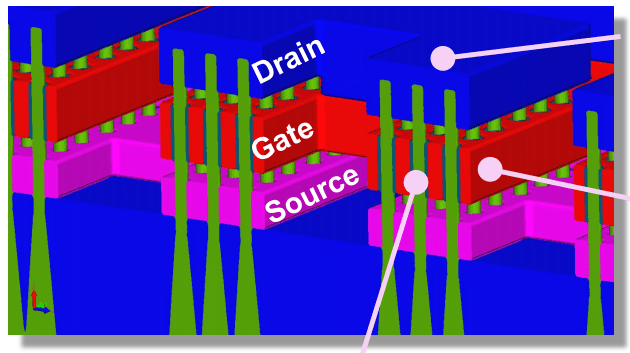

De 14nm- en 10nm-nodes zijn behoorlijk uitgekristalliseerd en de productiefaciliteiten van fabrikanten worden voorbereid op de massaproductie. Voor processors en andere rekeneenheden worden finfets gemaakt die bestaan uit silicium met een hkmg-techniek voor de gates. Een lastig punt zijn de metalen connectors om de transistors aan te sturen. Het is zeer moeilijk om die precies uit te lijnen met de transistors. Tot 14nm kan dat grotendeels via conventionele lithografie, maar daaronder moet overgestapt worden op automatische uitlijning.

Voorbij 10nm is zelfassemblage van de contacten een must en moet ook worden gezocht naar alternatieven voor silicium. De mobiliteit van ladingdragers is niet langer voldoende om in de kleine ruimtes de gewenste eigenschappen te realiseren, waardoor siliciumgermanium nodig is. Vanaf 7nm zouden zogeheten III-V-materialen moeten volgen en richting 5nm worden transistors waarschijnlijk niet meer liggend, maar staand aangebracht, met nanodraden.

Voorbij 10nm is zelfassemblage van de contacten een must en moet ook worden gezocht naar alternatieven voor silicium. De mobiliteit van ladingdragers is niet langer voldoende om in de kleine ruimtes de gewenste eigenschappen te realiseren, waardoor siliciumgermanium nodig is. Vanaf 7nm zouden zogeheten III-V-materialen moeten volgen en richting 5nm worden transistors waarschijnlijk niet meer liggend, maar staand aangebracht, met nanodraden.

Overstap naar euv?

Afmetingen en materialen kiezen voor de verschillende technologie-nodes is één ding, maar uiteraard moeten de transistors ook geproduceerd worden. De gangbare techniek om dat voor de huidige generatie te realiseren, is lithografie. Daarbij wordt een groot negatief van het waferoppervlak gemaakt: het masker, dat door een lichtbron en een lenzenstelsel verkleind op een wafer geprojecteerd wordt. Een fotogevoelige laag neemt het patroon over, waarna de belichte delen weggeëtst worden. Voor elke laag van een wafer wordt dit herhaald, wat leidt tot meerlaagse patronen die tussentijds allerlei bewerkingen als etsen, vullen en harden ondergaan.

Afmetingen en materialen kiezen voor de verschillende technologie-nodes is één ding, maar uiteraard moeten de transistors ook geproduceerd worden. De gangbare techniek om dat voor de huidige generatie te realiseren, is lithografie. Daarbij wordt een groot negatief van het waferoppervlak gemaakt: het masker, dat door een lichtbron en een lenzenstelsel verkleind op een wafer geprojecteerd wordt. Een fotogevoelige laag neemt het patroon over, waarna de belichte delen weggeëtst worden. Voor elke laag van een wafer wordt dit herhaald, wat leidt tot meerlaagse patronen die tussentijds allerlei bewerkingen als etsen, vullen en harden ondergaan.

Euv blijkt lastiger te implementeren dan voorheen gedacht

Momenteel wordt lithografie gerealiseerd met licht met een golflengte van 193nm, waarbij een laagje water tussen lenzen en wafer extra lichtbreking oplevert. Zo komt de techniek aan zijn naam, 193nm immersion lithography. Tot pakweg 45nm werkte dat goed, maar met kleinere nodes wordt het steeds lastiger om de zeer kleine details foutloos van het masker naar de wafer over te brengen. Vaak worden patronen dubbel belicht om dat voor elkaar te krijgen en zelfs zogeheten triple patterning zou noodzakelijk worden.

Licht met een kortere golflengte zou fijnere patronen mogelijk maken. Daarbij komt extreem ultraviolet licht, kortweg euv, kijken. Chipfabrikanten bereiden de overstap naar euv al lang voor, maar de techniek blijkt lastiger te implementeren dan voorheen gedacht. Vooral de lichtopbrengst valt vooralsnog tegen. Een minder felle uv-bron leidt tot langere belichtingstijden en dus tot een lagere productiesnelheid.

In de cleanroom van Imec is een euv-machine van ASML opgesteld, die gebruikt wordt om het euv-proces te optimaliseren. Eind 2013 moet met een lichtopbrengst van 80W een doorloopsnelheid van 58 wafers per uur gehaald worden. Eind 2014 moet dat verhoogd zijn naar 250W, dus zo'n 180 wafers per uur.

Euv-lithografie moet zijn intrede maken bij de overstap naar de 10nm-node. Tot die tijd zou 193nm-immersion volstaan, maar dan zou wel double patterning nodig zijn. Voor 10nm zou triple patterning met 193i nodig zijn, terwijl met euv single patterning mogelijk zou zijn. Tegen de tijd dat die overstap gemaakt moet worden, moet de lichtopbrengst in orde zijn.

/i/1383499536.jpeg?f=imagenormal)

Voorbij 10nm

De verwachte levensduur van traditionele lithografie lijkt op te houden na de 10nm-node. Ook euv lijkt dan niet langer in staat om features klein genoeg op de wafers te kunnen overbrengen of om dat kosteneffectief te doen. Daarmee zou euv slechts één node, die van 10nm, meegaan, maar de totale levensduur is natuurlijk veel langer, aangezien niet alles en iedereen direct op de nieuwste nodes kan overstappen.

Desalniettemin moet euv-lithografie rond 2015 of 2016 met 10nm zijn intrede doen, maar wat moet daarna gebeuren? Met de 7nm- en 5nm-nodes zou lithografie geen optie meer zijn, dus rond 2017 moet een alternatief beschikbaar zijn. Bij Imec wordt juist daarnaar naarstig onderzoek gedaan en worden technieken uitgeprobeerd.

Vanaf 5nm moeten meer exotische materialen de basis voor chips vormen

Een van de mogelijke alternatieven voor lithografie is een techniek die 'directed self assembly' genoemd wordt. Vanaf de 7nm-node zou dsa effectiever zijn dan lithografie, aangezien zelfs euv dan al double of triple patterning nodig zou hebben. Met dsa worden eerst grove structuren met lithografie gerealiseerd, waaraan vervolgens polymeren kunnen hechten. Zo kunnen kleinere structuren gerealiseerd worden dan met normale lithografische technieken.

Vanaf 5nm, naar verwachting rond 2019, moeten meer exotische materialen de basis voor chips gaan vormen. De ruimte tussen horizontaal aangelegde transistors zou dan te klein worden voor zaken als interconnects, reden om op verticale finfets over te stappen. Die moeten dan van germanium of III-V-halfgeleiders gemaakt worden. Bij Imec wordt daar al onderzoek naar gedaan en de eerste resultaten zijn er inmiddels.

Tegelijk worden de eerste experimenten uitgevoerd naar andere alternatieven, zoals quantum-spin-transistors, grafeen en andere 2d-materialen. Zo zijn fundamentele experimenten met zogeheten flakes uitgevoerd, waarbij transistors worden gemaakt van 'tweedimensionale' schilfers van molybdeendisulfide en wolfraamselenide. De schilfers zijn vooralsnog micrometers groot, maar moeten in de toekomst nanometer-grote gates vormen.

Tegelijk worden de eerste experimenten uitgevoerd naar andere alternatieven, zoals quantum-spin-transistors, grafeen en andere 2d-materialen. Zo zijn fundamentele experimenten met zogeheten flakes uitgevoerd, waarbij transistors worden gemaakt van 'tweedimensionale' schilfers van molybdeendisulfide en wolfraamselenide. De schilfers zijn vooralsnog micrometers groot, maar moeten in de toekomst nanometer-grote gates vormen.

De hoogte in: 3d-chips

De eerste stappen om op transistorniveau van horizontale bouw naar verticale bouw over te stappen zijn met finfets al gemaakt. In de toekomst kunnen verticale nanodraden met gates rondom leiden tot nog verdergaande verticale bouw, maar ook op chipniveau kan winst geboekt worden door de derde dimensie te benutten.

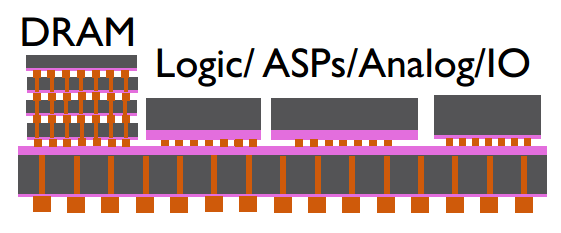

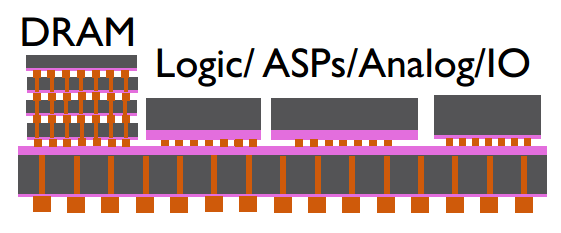

Het stapelen van chips wordt ook nu al gedaan, maar nog niet op de efficiëntste manier. Verschillende plakjes silicium, een 'die' in het jargon, worden opeengestapeld, maar de onderlinge verbindingen lopen buitenlangs. Dat levert relatief lange draden op, die verlies in energie, bandbreedte en kosten met zich meebrengen. Daarom wordt al geruime tijd onderzocht of de dies niet direct op elkaar aangesloten kunnen worden, met connectors in de chips die met elkaar in contact staan.

Het is een kwestie van balans tussen testkosten en hogere 3d-yields

Dergelijke through silicon via's, of tsv's heten zo omdat ze paden of via's vormen door het silicium heen. Dat levert korte communicatielijnen op, met alle voordelen van dien. Imec is er inmiddels in geslaagd tsv's van 5 micrometer doorsnede en 50 micometer lang te maken, die door het bulk-silicium steken. De koperen connectors worden daarbij van een tinnen uiteinde voorzien en met de koperen connector van de onderliggende laag verbonden. De onderlinge afstand tussen de connectors, ook bekend als de pitch, is momenteel zo'n 20 micrometer.

Gezien de vereiste precisie mag de afwijking, dus de mate waarin de twee te verbinden dies onderling verschoven zijn, niet meer dan 3 micrometer bedragen. Dat brengt een gevaar met zich mee voor stapelen; verkeerd uitgelijnde dies kunnen een 'stack' verpesten. Bovendien kan een defecte die een hele stack nutteloos maken, dus is het zaak om die vooraf te testen. Dat testen van dies kost echter tijd en geld, dus is het een kwestie van de juiste balans tussen testkosten en hogere 3d-yields.

/i/1383499985.png?f=imagenormal)

Stapelen heeft nog een risico; de chips kunnen hun warmte minder goed kwijt, wat vooral voor geheugenchips negatief is, aangezien dat de retentietijd vermindert. Een oplossing kan liggen in horizontale stacks, met een interposer die als onderliggend substraat en warmteafvoer dienstdoet. De interconnects zijn zo echter lastiger te realiseren dan met tsv's, maar door zeer smalle interconnects te maken kan de interconnectlengte gelijk aan de afstand tussen de dies gemaakt worden en is de routering eenvoudig.

Flexibele hardware

Nieuwe toepassingen vereisen steeds flexibelere hardware, letterlijk en figuurlijk. Dat letterlijke deel kennen we al een tijdje; in veel consumentenelektronica worden stukjes printplaat en soms zelfs het hele pcb van flexibel plastic gemaakt. De standaardcomponenten worden daarop geplakt en in het plastic zitten alleen passieve componenten, zoals printbanen. Dergelijke flexibele printplaatjes zijn echter niet bedoeld om veelvuldig bewogen te worden; printspoortjes zouden breken.

Voor echte toepassingen in consumentenelektronica is een display nodig

Een manier om printplaten niet alleen flexibel, maar ook rekbaar te maken, is het gebruik van polymeren. In materialen als siliconen of pdms kunnen printbanen beschermd worden en is de 'printplaat' rekbaar. Om ook de printbanen mee te laten rekken, kunnen ze als tweedimensionale veren worden geproduceerd. Zo kunnen bijvoorbeeld wearables, zoals intelligente patches gemaakt worden, maar voor echte toepassingen in consumentenelektronica is natuurlijk een display nodig.

De beeldschermtechniek die zich leent voor flexibele displays is oled, maar dan moeten wel enkele obstakels geslecht worden. Dergelijke displays moeten een voldoende hoge resolutie hebben, zuinig zijn en tegen de elementen bestand zijn. De flexibiliteit is dankzij het printen op een flexibel substraat mogelijk, maar dan moeten wel de aansturende tft's klein genoeg zijn om de oleds aan te sturen. Imec maakt gebruik van igzo-tft's en stuurt die digitaal aan. Dat levert een zuinige tft-matrix op om de oleds aan te sturen./i/1383500377.png?f=imagenormal)

De oleds en de onderliggende elektronica om ze aan te sturen moeten beschermd worden door laagjes beschermend materiaal om lucht, vocht en vuil tegen te houden. In samenwerking met het Holst Centre, een in Nederland gebaseerde spin-off van Imec, zijn inmiddels methodes ontwikkeld om die bescherming aan te brengen.

De laatste horde voor een brede beschikbaarheid van goedkope, flexibele oledschermen is massaproductie. Omdat de componenten, vooral de tft-transistors, zo klein zijn, is grote precisie nodig om de diverse stappen goed uit te lijnen met roll-to-roll-productie. Met sheet-to-sheet is die precisie makkelijker te realiseren, maar de productie is dan lager en dus duurder. Roll-to-roll-productie van flexibele oleds zou nog vijf jaar op zich laten wachten, zo voorspellen Imec en het Holst Centre.

Gezondheidszorg: meer en persoonlijke data

Vaak wordt bij berichtgeving rond research & development de vraag gesteld: wat heb ik er aan? Bij een van de onderzoeksrichtingen van Imec, en bij tal van andere grote r&d-afdelingen, is die vraag vrij eenvoudig te beantwoorden: het komt je gezondheid ten goede. De diverse initiatieven die bij Imec worden onderzocht moeten bepaalde ziekten namelijk niet alleen beter kunnen bestrijden, maar ze ook helpen voorkomen en in een vroeg stadium identificeren./i/1383500657.jpeg?f=imagenormal)

Een van de methodes om dat laatste mogelijk te maken is de Cell Sorter, die door Imec is ontwikkeld. Dit lab on a chip kan cellen uit een druppel bloed sorteren en interessante cellen voor verdere analyse bewaren. Bloed met cellen wordt daartoe door een 30 micrometer breed kanaal met daarin een laser en eronder een cmos-sensor geleid. Een cel wordt aan de hand van het interferentiepatroon met laserlicht door de cmos-sensor herkend en kan dan specifieke kamers worden ingeleid. De cellen worden gestuurd door met kleine microheaters warmtebubbels te maken, die de cellen een bepaalde richting opstuwen. Zo kunnen kankercellen in een vroeg stadium en met minimale moeite herkend worden.

Met supercomputers kan de werking van moleculen als medicijn voorspeld worden

De sensortechniek is afgeleid van de techniek om defecten op wafers te herkennen en verwerkt twintig miljoen beeldjes per seconde. De microheaters zijn vergelijkbaar met de koppen van een inktjetprinter. Door lithografische productiemethodes kunnen de Cell Sorters duizenden kanalen bevatten en massaal geproduceerd worden.

Behalve aan de Cell Sorter wordt ook gewerkt aan andere hardware voor persoonlijke gezondheidszorg. Zo worden wegwerppleisters ontwikkeld die vitale functies als ademhaling en hartslag in de gaten houden en daarover rapporteren.

Ook onderzoek naar geneesmiddelen profiteert van technologie. Met supercomputers kan de werking van moleculen als medicijn voorspeld worden en kunnen kandidaatmoleculen snel gescand worden. Daarvoor is niet alleen de nodige rekenkracht nodig, maar ook de juiste software. Tijdens het ITF kondigden Imec en Intel een samenwerkingsverband aan met een farmaceutisch bedrijf en universiteiten om niet alleen hardware, maar ook software voor lifesciences te ontwikkelen. Dat moet onder meer leiden tot betere simulaties van weefsels, medicijnen en snellere manieren om genetische informatie in kaart te brengen./i/1383500981.jpeg?f=imagenormal)

Dat laatste kan op zijn beurt gebruikt worden om gerichter ziektes te bestrijden. In plaats van een breed werkend medicijn, dat niet specifiek voor een patiënt is, te gebruiken, kan medicatie veel gerichter worden toegediend als de genetische informatie van ziektes en patiënten bekend is. Het human genome project deed daar aanvankelijk jaren over en kostte miljoenen, maar inmiddels kan het binnen enkele dagen voor duizend euro. Als dat verder omlaag gebracht kan worden naar uren en minder dan honderd euro, kunnen patiënten veel gerichter worden geholpen.

/i/1383495458.jpeg?f=imagenormal)

/i/1383495891.png?f=imagenormal)

Voorbij 10nm is zelfassemblage van de contacten een must en moet ook worden gezocht naar alternatieven voor silicium. De mobiliteit van ladingdragers is niet langer voldoende om in de kleine ruimtes de gewenste eigenschappen te realiseren, waardoor siliciumgermanium nodig is. Vanaf 7nm zouden zogeheten III-V-materialen moeten volgen en richting 5nm worden transistors waarschijnlijk niet meer liggend, maar staand aangebracht, met nanodraden.

Voorbij 10nm is zelfassemblage van de contacten een must en moet ook worden gezocht naar alternatieven voor silicium. De mobiliteit van ladingdragers is niet langer voldoende om in de kleine ruimtes de gewenste eigenschappen te realiseren, waardoor siliciumgermanium nodig is. Vanaf 7nm zouden zogeheten III-V-materialen moeten volgen en richting 5nm worden transistors waarschijnlijk niet meer liggend, maar staand aangebracht, met nanodraden. Afmetingen en materialen kiezen voor de verschillende technologie-nodes is één ding, maar uiteraard moeten de transistors ook geproduceerd worden. De gangbare techniek om dat voor de huidige generatie te realiseren, is lithografie. Daarbij wordt een groot negatief van het waferoppervlak gemaakt: het masker, dat door een lichtbron en een lenzenstelsel verkleind op een wafer geprojecteerd wordt. Een fotogevoelige laag neemt het patroon over, waarna de belichte delen weggeëtst worden. Voor elke laag van een wafer wordt dit herhaald, wat leidt tot meerlaagse patronen die tussentijds allerlei bewerkingen als etsen, vullen en harden ondergaan.

Afmetingen en materialen kiezen voor de verschillende technologie-nodes is één ding, maar uiteraard moeten de transistors ook geproduceerd worden. De gangbare techniek om dat voor de huidige generatie te realiseren, is lithografie. Daarbij wordt een groot negatief van het waferoppervlak gemaakt: het masker, dat door een lichtbron en een lenzenstelsel verkleind op een wafer geprojecteerd wordt. Een fotogevoelige laag neemt het patroon over, waarna de belichte delen weggeëtst worden. Voor elke laag van een wafer wordt dit herhaald, wat leidt tot meerlaagse patronen die tussentijds allerlei bewerkingen als etsen, vullen en harden ondergaan./i/1383499536.jpeg?f=imagenormal)

Tegelijk worden de eerste experimenten uitgevoerd naar andere alternatieven, zoals quantum-spin-transistors, grafeen en andere 2d-materialen. Zo zijn fundamentele experimenten met zogeheten flakes uitgevoerd, waarbij transistors worden gemaakt van 'tweedimensionale' schilfers van molybdeendisulfide en wolfraamselenide. De schilfers zijn vooralsnog micrometers groot, maar moeten in de toekomst nanometer-grote gates vormen.

Tegelijk worden de eerste experimenten uitgevoerd naar andere alternatieven, zoals quantum-spin-transistors, grafeen en andere 2d-materialen. Zo zijn fundamentele experimenten met zogeheten flakes uitgevoerd, waarbij transistors worden gemaakt van 'tweedimensionale' schilfers van molybdeendisulfide en wolfraamselenide. De schilfers zijn vooralsnog micrometers groot, maar moeten in de toekomst nanometer-grote gates vormen.

/i/1383499985.png?f=imagenormal)

/i/1383500377.png?f=imagenormal)

/i/1383500657.jpeg?f=imagenormal)

/i/1383500981.jpeg?f=imagenormal)

:strip_icc():strip_exif()/i/2005184414.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2005169150.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2003043920.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2001550947.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2001508423.jpeg?f=fpa_thumb)

/i/2001190117.png?f=fpa_thumb)

:strip_exif()/i/2005283572.jpeg?f=fpa)

/i/1304670251.png?f=fpa)

:strip_exif()/i/1329312935.jpeg?f=fpa)

/i/2001435495.png?f=fpa)

/i/1383492957.png?f=fpa)

/i/1242207182.png?f=fpa)

:strip_exif()/i/1152627031.gif?f=fpa)