Introductie: Tick-Tock

Intel heeft tijdens de 2012-editie van zijn Developer Forum, beter bekend als IDF, uitgebreid laten zien hoe Haswell, de nieuwe generatie processors voor 2013, in elkaar zit. Een van de belangrijkste aandachtspunten voor de nieuwe processors is het energieverbruik. Samen met de verbeterde prestaties van de in de processor ingebakken gpu, ook bekend als processor graphics, moet Haswell zuiniger zijn dan Ivy Bridge en grafisch een stuk beter presteren.

Zoals bekend hanteert Intel al jaren het zogeheten Tick-Tock-model, waarbij een Tock, ofwel de introductie van een nieuwe processorarchitectuur, wordt afgewisseld met een Tick, een procesverkleining waarbij transistors volgens een nieuw procedé vervaardigd worden. Sandy Bridge vormde de laatste Tock en werd op 32nm gemaakt. De opvolger Ivy Bridge werd op 22nm gemaakt en vormde dus de Tick. Haswell volgt Ivy Bridge weer op en logischerwijs is het tijd voor een Tock.

/i/1347729332.png?f=imagenormal)

Dat betekent dat Haswell nog steeds op 22nm geproduceerd zal worden en gebruik zal maken van de zogeheten trigate-transistors. Wel is het procedé waarmee de 22nm-transistors gemaakt worden verbeterd, wat deels de oorzaak zou zijn van het verminderde energieverbruik.

Dat is echter maar een deel van het verhaal; de cpu-cores van Haswell werden grondig onder handen genomen en moeten flinke prestatieverbeteringen opleveren. Intel heeft echter zijn aandacht vooral gericht op de gpu; die moet tweemaal de prestaties van de gpu van Ivy Bridge leveren. Intel had immers beloofd een inhaalslag te leveren om een ooit ondergeschoven kindje concurrerend te maken met losse videokaarten.

Haswell moet Intels ultrabook-platform aantrekkelijker en krachtiger maken. Sinds de introductie van het ultrabook-segment, met Sandy Bridge-processors, heeft Ivy Bridge de prestaties opgeschroefd en Haswell moet dat verder uitbouwen. Ook krijgen ultrabooks in de nabije toekomst alternatieve interactiemogelijkheden, zoals spraakbesturing, gebaren- en gezichtsherkenning. Daarvoor is uiteraard extra, al dan niet grafisch, rekenvermogen nodig.

Haswell: wijzigingen in de cpu-architectuur

Haswell wordt net als Ivy Bridge op 22nm geproduceerd, maar krijgt een aantal verbeteringen in de architectuur; het is immers een Tock-generatie, wat een nieuwe architectuur met zich meebrengt.

Haswell wordt net als Ivy Bridge op 22nm geproduceerd, maar krijgt een aantal verbeteringen in de architectuur; het is immers een Tock-generatie, wat een nieuwe architectuur met zich meebrengt.

We beginnen met de algemene opbouw van een Haswell-processor. Op het eerste gezicht is er weinig veranderd ten opzichte van Ivy Bridge; de cores worden door middel van een ring met elkaar en met de smart cache verbonden, en ook de gpu en system agent worden door dezelfde ring bediend. De bandbreedte van de ringarchitectuur is echter verdubbeld, waardoor het cachegeheugen sneller benaderd kan worden. Ook de toegang tot de system agent is efficiënter gemaakt.

Om de prestaties verder op te schroeven krijgt Haswell diepere queue-depths naar het ram-geheugen.

De grootste verbeteringen zitten echter in de cores zelf. Die krijgen meer execution units dan in Ivy Bridge, maar hoeveel meer wordt nog niet bekendgemaakt. Wel is duidelijk dat de eu's twee extra poorten krijgen; in plaats van de zes stuks van Ivy Bridge zijn er nu acht. Een extra integer-alu en branch-unit op de nieuwe poort 6 maakt de alu van poort 0 en 1 vrij om met vectoren aan de slag te gaan. Poorten 2 en 3 worden vrijgemaakt door de nieuwe address generation unit op poort 7, waardoor voortaan twee load- en een store-operatie per kloktik kunnen worden uitgevoerd.

De grootste verbeteringen zitten echter in de cores zelf. Die krijgen meer execution units dan in Ivy Bridge, maar hoeveel meer wordt nog niet bekendgemaakt. Wel is duidelijk dat de eu's twee extra poorten krijgen; in plaats van de zes stuks van Ivy Bridge zijn er nu acht. Een extra integer-alu en branch-unit op de nieuwe poort 6 maakt de alu van poort 0 en 1 vrij om met vectoren aan de slag te gaan. Poorten 2 en 3 worden vrijgemaakt door de nieuwe address generation unit op poort 7, waardoor voortaan twee load- en een store-operatie per kloktik kunnen worden uitgevoerd.

Haswells eu's hebben twee fma's, fused multiply/add-eenheden, extra gekregen en de floating-pointprestaties moeten met een extra multiply-eenheid verder worden verbeterd. De dubbel zo grote bandbreedte van de L1- en L2-caches moet data snel genoeg kunnen aanleveren om de fma's bezig te houden.

/i/1347732612.png?f=imagenormal)

De met Sandy Bridge geïntroduceerde avx-instructieset werd in Haswell uitgebouwd tot een volledig 256bit brede avx2-instructieset. De single en double precision floating point-prestaties per core zijn daarmee verdubbeld, en de latencies en precisie zijn eveneens sterk verbeterd. Het vertalen van integercode naar avx-instructies is eenvoudiger geworden, waardoor dergelijke code ook gevectoriseerd kan worden en door de snelle avx2-hardware kan worden uitgevoerd.

Haswell kreeg bovendien instructies om data in registers en geheugens parallel te benaderen zonder op threads te hoeven wachten; de nieuwe Transactional Synchronisation Extensions, TSX, moeten daarvoor zorgen. Ook de ondersteuning voor versleuteling werd drastisch verbeterd, waardoor onder meer versleutelde harde schijven of ssd's sneller moeten worden. Ten slotte is de ondersteuning voor virtualisatie aangepast; de latencies om met de hardware te communiceren zijn kleiner.

De grafische processor: sneller en schaalbaar

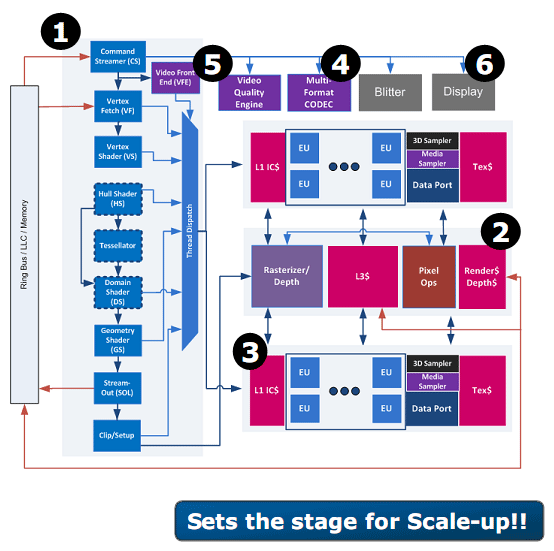

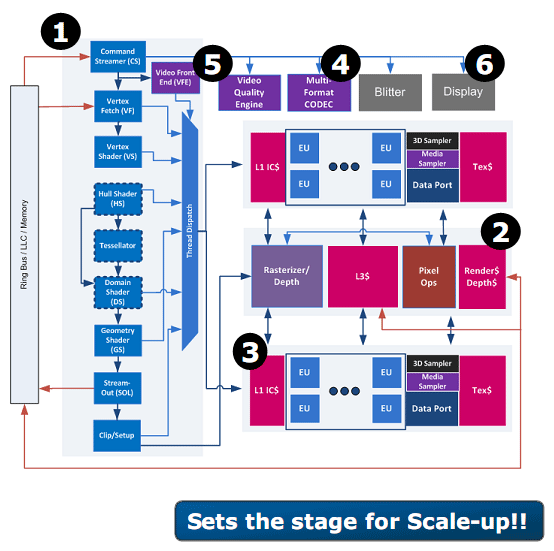

Niet alleen de cpu-cores van Haswell zijn flink onder handen genomen, de geïntegreerde gpu, ook bekend als processor graphics of pgfx, of simpelweg de gpu, is eveneens verbeterd. Zoals bekend krijgt Haswell drie varianten: de GT1, GT2 en GT3. Bij de GT1 en GT2 gaat het om dezelfde hardware met verschillende aantallen execution units; de GT3 is de meest high-end variant, met de meeste eu's.

Het voorbereidende werk voor de Haswell-gpu is grotendeels bij de Ivy Bridge-generatie gerealiseerd. De modulaire opbouw van de gpu's in zogeheten slices is in Haswell voortgezet en bestaat uit zes domeinen. De eerste slice is de front-end, die werklasten voor de gpu voorbereidt. De slice common en sub-slice bevatten respectievelijk onder meer de caches en eu's. De vierde slice bevat video codec-hardware, de vijfde is voor logica om de videokwaliteit te verbeteren en nummer zes is, als laatste slice, verantwoordelijk voor de displays.

Om met die laatste slice te beginnen; de Haswell-gpu kan drie beeldschermen onafhankelijk van elkaar aansturen en ondersteunt een maximale resolutie van 4k, oftewel 4096x2160 pixels. De front-end, of slice 1, moet voor de GT3-versie tweemaal zo snel werken als voor de GT1 en GT2; er moeten immers tweemaal zo veel eu's van instructies worden voorzien. Een nieuwe feature in de front-end is de resource streamer in de command streamer, die aanzienlijke verbeteringen moet opleveren door de drivers te ontlasten.

/i/1347733356.png?f=imagenormal)

De caches uit de slice common zijn gedeeld tussen de eu's, maar worden dynamisch gealloceerd. De eu's moeten op ruim 1GHz draaien.

Naast de ondersteuning voor 4k-displays krijgt de Haswell-gpu ook directx 11-ondersteuning en moet de gpu de low-end tot midrange-videokaarten kunnen vervangen. Een flink aantal mediacodeer- en -decodeerbewerkingen wordt in de hardware uitgevoerd, wat een efficiëntere verwerking van de load moet opleveren. Zo kreeg Haswell een hardwarematige, scalable video coding-codec, een hardwarematige mjpeg-decoder en dito mpeg2-encoder. Ten slotte zijn zaken als videopostprocessing verbeterd en voegde Intel beeldstabilisatie aan videobeelden toe.

Powermanagement: een nieuwe slaapstand

Zoals beloofd kijken we uitgebreid naar de verbeteringen in energieverbruik van Haswell. De aanpassingen in de cpu- en gpu-cores die snelheidswinst opleveren, brengen vanzelf al energiebesparingen mee; de processor is immers sneller klaar met een bepaalde taak, waarna hij in een energiezuinige modus kan worden geschakeld.

Een van de belangrijkste nieuwe features daarbij is een nieuwe slaapstand. Vooral ultrabooks zouden daar profijt van hebben, maar ook desktops verstoken minder energie als ze sneller en 'agressiever' slapen. Nadeel van een slaapstand was altijd dat het veel tijd kost om uit een oppervlakkige slaapstand te ontwaken. Een nieuwe S0-staat, S0ix, moet daarin verandering brengen.

Zoals bekend is de S0-toestand van een processor de actieve toestand, terwijl S3 en S4 energiebesparende slaapstanden zijn. Tijdens S4 zijn de meeste processoronderdelen uitgeschakeld en krijgen die geen spanning. Bij belasting duurt het echter even om de cpu wakker te krijgen, terwijl de cpu in de S0-staat zeer responsief is, maar spanning op de componenten heeft en dus relatief veel energie verstookt. De nieuwe S0ix-modus, door Intel 'active idle' genoemd, vormt een overgang tussen S0 en S4, en combineert het beste van beide toestanden. De meeste spanning is uitgeschakeld, maar het systeem reageert nog altijd zeer snel als er vraag is.

/i/1347733467.png?f=imagenormal)

De S0ix-active idle-toestand maakt Intels belofte van 'connected standby' mogelijk, waarbij een ultrabook in diepe slaap is, maar wel mailtjes en social media-berichten kan ontvangen. De schakeltijd tussen S0ix en S0 zou in de orde liggen van milliseconden, terwijl het opgenomen vermogen in idle-toestand slechts 5mW zou bedragen. De nieuwe S0ix-modus is transparant voor het besturingssysteem te gebruiken.

Intel heeft ook traditionelere maatregelen genomen om energie te besparen. Zo wordt intensief geschakeld tussen energiemodi. De latencies van de verschillende C-states, die aangeven in hoeverre onderdelen van de processor actief zijn, zijn met 25 procent verkleind en meer onderdelen kunnen van de spanning worden losgekoppeld. Een van de belangrijkste verbeteringen daarbij is de ontkoppeling van de cores van de cache- en ringspanningen. Een core kan dus volledig worden uitgeschakeld, terwijl een andere core en bijbehorend cache-geheugen nog actief zijn.

Ook andere onderdelen, zoals de voltage regulators, zijn onder handen genomen en zuiniger gemaakt. De communicatie tussen processor en pch, voorheen de 'southbridge', is zuiniger, net als de chipset zelf. Op deze zogeheten platformpower gaan we op de volgende pagina dieper in.

Platformpower: de som der delen

Op de vorige pagina haalden we het al even aan; platformpower is het geheel van alle onderdelen van de processor en bijbehorende onderdelen. Een flinke besparing kan worden behaald door het geheugen zuiniger te maken. Meer en slimmer cache kan daaraan bijdragen; er hoeft dan immers minder met het dram gecommuniceerd te worden. Ook de spanningen die door de pch gebruikt worden, kunnen worden verlaagd. In de eerste plaats moet Haswell geen 65nm-chipset meer krijgen, maar wordt deze eindelijk volgens een moderner procedé gemaakt. Dat staat lagere spanningen op de onderdelen toe en ook de interfaces van de pch of platform controller hub, zoals die voor usb, sata en pci-express, zijn lager. Als geen data over die interfaces verstuurd wordt, kunnen de controllers worden uitgeschakeld.

/i/1347733572.png?f=imagenormal)

Speciale aandacht verdient het beeldscherm. Intel liet een jaar geleden tijdens het IDF zijn panel self refresh-technologie zien. Deze psr laat een statisch beeld op het scherm staan, dat uit een klein stukje geheugen in het paneel zelf wordt gebufferd. De gpu hoeft dan geen 60fps statisch beeld te renderen en kan in slaapstand. Dat moet aanzienlijke energiebesparingen opleveren.

De GTx-gpu wordt binnen de energiebeperkingen van een laptop intelligent aangestuurd. Daarbij wordt de maximale framerate gezocht bij een zo laag mogelijke werkspanning. Doel daarvan is primair het aandeel van de lekspaningen in de gpu te beperken en het functionele vermogen te maximaliseren. Bovendien kan bij de GT3 een slice worden uitgeschakeld, waardoor deze veelal hetzelfde vermogen verstookt als de GT2. Volgens Intel resulteert dat in een Haswell-processor die met 17W dezelfde prestaties levert als Ivy Bridge met 35W. Die tdp moet overigens nog verder omlaag, tot 10W voor sommige processors.

Als Windows 8 dit najaar op de markt verschijnt, zou het energiebeheer van de Haswell-architectuur nog beter tot zijn recht komen. De in Windows 7 ingezette methode om activiteiten samen te voegen, zoals interrupts van het besturingssysteem en overige interrupts, wordt uitgebreid. In Windows 7 is de interval tussen de zogeheten system timer ticks 15,6ms. Dat geeft de cpu nauwelijks de gelegenheid in een slaapstand te gaan, hoewel Windows 7 de activiteit wel rond deze ticks centreert. In Windows 8 zijn deze system timer ticks echter verdwenen, zodat het systeem veel langer kan slapen.

/i/1347733620.png?f=imagenormal)

Het complete systeem, van processor en pch tot hardware van derden, kan bovendien met Power Optimizer worden geoptimaliseerd om zo weinig mogelijk energie te verstoken. Daartoe worden technieken als S0ix, en de slaapstanden van de pch en overige componenten verenigd. Dit framework zou gezien moeten worden als de opvolger van acpi. De diverse activiteiten van alle componenten zouden daarmee worden geanalyseerd en gesynchroniseerd, zodat de processor zo lang mogelijk idle en dus in slaapstand kan worden gehouden.

Conclusie: even geduld aub

Haswell heeft tal van verbeteringen aan boord, zowel op het gebied van architectuur voor de cpu-cores en de gpu, als op het vlak van energiebeheer. De transistors worden net als de Ivy Bridge-generatie nog op 22nm gebakken, maar voortschrijdend inzicht maakt de transistors zuiniger.

Een grotere rol speelt het verbeterde, agressieve energiebeheer van zowel de cpu als de gpu. De nieuwe energietoestand, S0ix, moet daar sterk aan bijdragen, maar ook de fijnere controle over spanningen, en het loskoppelen van de core-spanningen van die van de ring en cache zijn flinke besparende maatregelen.

Op het gebied van architectuur heeft Intel een flinke verbetering beloofd, allereerst met meer eu's voor de cores en twee extra poorten in die eu's. De extra fma's, nieuwe instructies en snellere caches moeten de cores aanzienlijk sneller maken. Ook de gpu moet weer een flinke stap maken en volgens Intel tweemaal zo snel worden als Ivy Bridge.

Pc's en dan vooral ultrabooks die met Haswell-processors worden uitgerust, lijken sneller, zuiniger, koeler en dus platter te kunnen worden. Voordat het echter zover is, zal Intel flink aan de productie moeten en kunnen wij tot midden 2013 alleen afwachten.

/i/1347729332.png?f=imagenormal)

Haswell wordt net als Ivy Bridge op 22nm geproduceerd, maar krijgt een aantal verbeteringen in de architectuur; het is immers een Tock-generatie, wat een nieuwe architectuur met zich meebrengt.

Haswell wordt net als Ivy Bridge op 22nm geproduceerd, maar krijgt een aantal verbeteringen in de architectuur; het is immers een Tock-generatie, wat een nieuwe architectuur met zich meebrengt. De grootste verbeteringen zitten echter in de cores zelf. Die krijgen meer execution units dan in Ivy Bridge, maar hoeveel meer wordt nog niet bekendgemaakt. Wel is duidelijk dat de eu's twee extra poorten krijgen; in plaats van de zes stuks van Ivy Bridge zijn er nu acht. Een extra integer-alu en branch-unit op de nieuwe poort 6 maakt de alu van poort 0 en 1 vrij om met vectoren aan de slag te gaan. Poorten 2 en 3 worden vrijgemaakt door de nieuwe address generation unit op poort 7, waardoor voortaan twee load- en een store-operatie per kloktik kunnen worden uitgevoerd.

De grootste verbeteringen zitten echter in de cores zelf. Die krijgen meer execution units dan in Ivy Bridge, maar hoeveel meer wordt nog niet bekendgemaakt. Wel is duidelijk dat de eu's twee extra poorten krijgen; in plaats van de zes stuks van Ivy Bridge zijn er nu acht. Een extra integer-alu en branch-unit op de nieuwe poort 6 maakt de alu van poort 0 en 1 vrij om met vectoren aan de slag te gaan. Poorten 2 en 3 worden vrijgemaakt door de nieuwe address generation unit op poort 7, waardoor voortaan twee load- en een store-operatie per kloktik kunnen worden uitgevoerd./i/1347732612.png?f=imagenormal)

/i/1347733356.png?f=imagenormal)

/i/1347733467.png?f=imagenormal)

/i/1347733572.png?f=imagenormal)

/i/1347733620.png?f=imagenormal)

:strip_icc():strip_exif()/i/1370069695.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/1325102159.jpeg?f=fpa_thumb)

/i/1367481289.png?f=fpa)

/i/1347385226.png?f=fpa)

:strip_exif()/i/1223397212.gif?f=fpa)

/i/1242207182.png?f=fpa)

/i/1346341868.png?f=fpa)

/i/1325597952.png?f=fpa)

/i/1340793687.png?f=fpa)

:strip_exif()/i/1035733687.gif?f=fpa)

/i/1293792521.png?f=fpa)

/i/1294416060.png?f=fpa)