Een nieuw materiaal zou het mogelijk maken chips met een feature-size van 20nm te produceren. De chemicaliën leveren een nieuwe fotoresist die met euv- lithografie gebruikt kan worden. In 2013 zou de techniek gebruikt kunnen worden.

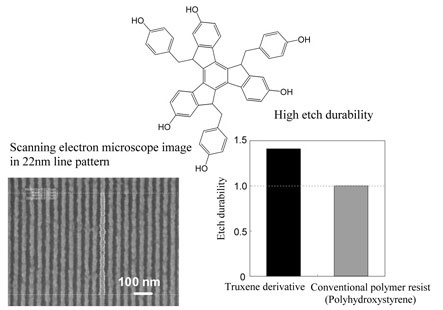

De Japanse elektronicagigant Toshiba heeft een derivaat ontwikkeld van een chemische substantie die vaker in de halfgeleiderindustrie gebruikt wordt, truxeen. Deze stof kan als fotoresist worden gebruikt bij de productie van halfgeleiders, waarbij de substantie compatibel is met euv-techniek. Een fotoresist wordt in de halfgeleiderindustrie gebruikt om het patroon van de toekomstige chip te vormen: het lichtgevoelige patroon dat door de fotoresist gevormd wordt, zorgt voor de overdracht van de halfgeleiderstructuren van het masker naar het silicium.

De huidige technieken voor de productie van chips zouden ontoereikend voor een schaalverkleining tot 20nm zijn, zo stelt Toshiba. De argonfluoride-lasers die samen met fotoresists voor de productie van lsi-chips gebruikt worden, zullen rond 2013 vervangen zijn door extreem ultraviolet-lithografie en het truxeen-derivaat als fotoresist. De truxeen-verbindig heeft enkele gewilde eigenschappen voor een toepassing als fotoresist: zo is het materiaal zeer fijn en robuust van structuur, en kan het voor zowel positieve als negatieve resist ingezet worden. Toshiba zal de techniek op 19 november tijdens het 22ste International Microprocesses and Nanotechnology Conference presenteren.

:strip_exif()/i/1257241493.gif?f=fpa)

/i/1247738571.png?f=fpa)

/i/1242377654.png?f=fpa)

:strip_exif()/i/1046975813.jpg?f=fpa)

/i/1266945034.png?f=fpa)

/i/1240844012.png?f=fpa)

/i/1262870626.png?f=fpa)

/i/1253695573.png?f=fpa)

/i/1250157415.png?f=fpa)

/i/1228478403.png?f=fpa)

/i/1217925693.png?f=fpa)

/i/1242207182.png?f=fpa)

/i/1240825121.png?f=fpa)