Rambus en Kingston hebben gezamenlijk een nieuwe variant van ddr3-geheugen ontwikkeld die beter zou presteren in combinatie met multicore-processors. Het threaded geheugen zou efficienter en zuiniger zijn.

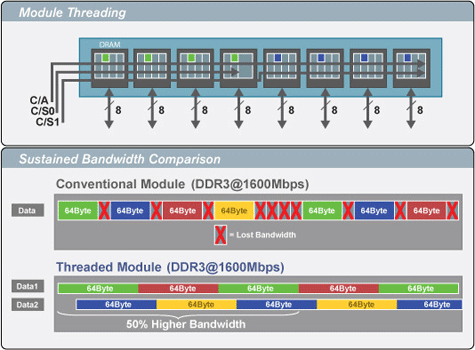

De beide geheugenfabrikanten hebben samengewerkt bij de ontwikkeling van een prototype geheugenmodule die de databus van de geheugeninterface beter benut. Waar reguliere ddr3-modules een deel van de beschikbare bandbreedte verloren laten gaan, moeten de threaded memory modules, zoals het geheugen gedoopt is, de volledige bandbreedte benutten. Het prototype tmm, dat Kingston en Rambus tijdens het Intel Developer Forum zullen demonstreren, zou vijftig procent efficienter zijn dan conventioneel geheugen.

Aangezien de geheugenmodules dankzij de nieuwe techniek eerder dan gewone ddr3-modules weer inactief kunnen worden, blijft het energieverbruik van de tmm's laag. Hierdoor zou ten opzichte van reguliere modules een besparing van twintig procent mogelijk zijn. De techniek is gebaseerd op reguliere ddr3-modules, maar beide 'helften' van elke module worden parallel aangesproken. Voor gebruik van tmm's is naar alle waarschijnlijkheid geen aanpassing van het moederbord nodig.

Wel zijn de printplaten van tmm's iets complexer en moeten nieuwe geheugencontrollers gebruikt worden om de dimm's threaded aan te spreken. Daar zowel AMD als Intel de geheugencontroller van het moederbord naar de cpu hebben verplaatst, zouden de processorfabrikanten licentiekosten aan Rambus moeten betalen: of threaded memory modules gemeengoed zullen worden, zal dan ook voor een deel van hen afhankelijk zijn.

/i/1244970021.png?f=fpa)

/i/1246105319.png?f=fpa)

/i/1262870626.png?f=fpa)

/i/1239556832.png?f=fpa)

/i/1282040928.png?f=fpa)

:strip_exif()/i/1196085296.gif?f=fpa)