Tick+

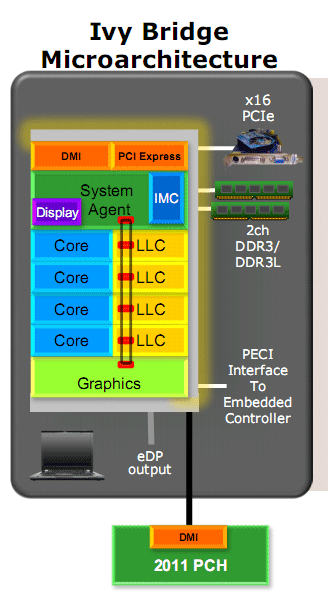

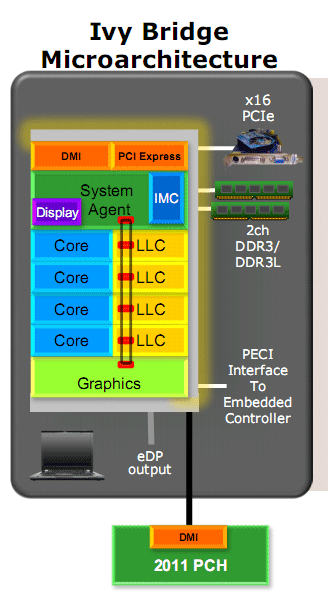

Intel hanteert sinds ongeveer vijf jaar het tick-tock-principe; een nieuwe microprocessorarchitectuur, of tock, wordt afgewisseld door een tick, ofwel een nieuw procedé om de chips te vervaardigen. Sandy Bridge vormde in 2010 de tock en Ivy Bridge moet, met een verkleining naar 22nm, de tick vormen. Volgens Intel is Ivy Bridge echter meer dan een tick; het zou een tick+ worden.

In plaats van simpelweg een procedé-verkleining van 32 naar 22nm moet Ivy Bridge een aantal flinke verbeteringen met zich meebrengen. De verbeteringen in de Ivy Bridge-chips zouden niet alleen in de architectuur van de cores, maar vooral ook in de grafische component te vinden zijn.

/i/1316954865.png?f=imagenormal)

De shrink naar 22nm is niet alleen een stap naar een kleiner procedé; met de overstap naar 22nm introduceert Intel ook zijn 'tri-gate'- of 3d-transistors. Deze nieuwe manier om de bouwstenen van de Ivy Bridge-chips te produceren kan enerzijds leiden tot zuinigere processors en anderzijds tot snellere chips.

Op de volgende pagina's bekijken we de vernieuwingen die Intel tijdens het Intel Developer Forum bekendmaakte. Of dat alle nieuwe features zijn die Ivy Bridge met zich meebrengt, blijkt pas als Intel de nieuwe generatie processors uitbrengt. Daarop moeten we echter nog wachten tot de eerste helft van 2012.

22nm en tri-gates

Waar Sandy Bridge nog op 32nm geproduceerd werd, zijn de feature-sizes van Ivy Bridge gereduceerd tot 22nm. Een kleinere transistor werkt met hogere snelheden tussen aan- en uitschakelen. Het is echter niet zo eenvoudig om de transistors te verkleinen, niet alleen wegens lithografische moeilijkheden, maar ook wegens natuurkundige verschijnselen. Een kleinere transistor heeft meer last van lekstromen, onder meer omdat de gates steeds dunner worden.

In het verleden bood Intel deze problemen het hoofd door met de stap naar 90nm-transistors zogeheten strained silicon te gebruiken, waardoor hogere stromen binnen de transistors gebruikt konden worden. Bij 65nm werden siliciumoxide en polysilicium gebruikt voor de gate. De 'high-k metal gate'-techniek werd bij de overstap naar 45nm geïntroduceerd. De gates konden dankzij deze technieken steeds kleiner worden en konden hogere stuurspanningen aan, maar voor de stap naar 22nm was een nieuwe techniek nodig: de tri-gate.

/i/1316954936.png?f=imagenormal)

De channel, de verbinding tussen de source en de drain, werd van de gate gescheiden door een dunne laag high-k-diëlektrum. Dat was in ieder geval zo tot bij de 45nm-transistors. Deze isolerende laag vergroot de elektrische capaciteit van de gate en laat zo hogere stuurstromen en schakelsnelheden toe. Voor 22nm-transistors bleek dit echter ook ontoereikend en er moest een manier worden gevonden om het geleidende kanaal te vergroten.

De oplossing bleek te liggen in het gebruik van een driedimensionale structuur. Het silicium van de channels werd omhoog gebracht als een verticale rib en daaromheen werd een laag high-k-diëlektrum aangebracht. Een eenvoudig rekensommetje leert dat, afhankelijk van de hoogte van de ribben, het contactoppervlak tussen gate en channel ruwweg verdubbelt. Door verscheidene ribben te gebruiken, kan zelfs nog meer winst geboekt worden en kunnen nog hogere stuurspanningen gebruikt worden.

De tri-gates die voor de Ivy Bridge-processors werden ontwikkeld brengen meer voordelen met zich mee. Niet alleen kunnen hogere stromen worden gebruikt, waardoor de transistors sneller kunnen schakelen en waardoor dus betere prestaties mogelijk zijn, ook het energieverbruik kan gereduceerd worden. Bij gelijkblijvende stuurstromen zijn de prestaties beter dan bij de 32nm-Sandy Bridge-processors, maar bij gelijke prestaties dalen de stromen en dus het opgenomen vermogen.

/i/1316955077.png?f=imagenormal)

Zo kan gekozen worden voor zuinigere of snellere processors, met gradaties daartussen. Volgens Intel zouden de 22nm-processors zelfs bij gelijke prestaties met de helft minder vermogen toekunnen. Ook de lekstromen, die in hoge mate het verbruik in idle-toestand bepalen, zijn in de tri-gate-transistors lager, waardoor langere stand-by-tijden voor laptops en zuinigere processors gerealiseerd kunnen worden.

De microarchitectuur

De fysieke veranderingen in de Ivy Bridge-processors zijn één facet van de nieuwe chips, de bouwstenen waarmee de Ivy Bridge-processors worden gemaakt zijn een ander, belangrijk aspect. Ook daarin zijn verbeteringen aangebracht, waarmee Intel zijn 'tick+'-omschrijving kracht bijzet.

Wat prestaties betreft werden onder meer de pipelines en de geheugenadressering aangepakt. De hyperthreading cores in Sandy Bridge deelden een buffer, maar singlethreaded toepassingen konden slechts de halve buffer benutten. De verdeling van de resources is dynamisch in Ivy Bridge, zodat alle beschikbare hardware daadwerkelijk benut kan worden.

De divider tussen integer- en floating point-berekeningen heeft tweemaal zo veel doorvoercapaciteit als die in Sandy Bridge, waardoor voornamelijk floating point-berekeningen sneller zouden worden. Instructies in de registers worden eveneens efficiënter opgeslagen, waardoor de executie-units werklasten sneller kunnen uitvoeren.

Ook beveiliging krijgt een update in Ivy Bridge, met onder meer een nieuwe random number generator, een belangrijk onderdeel voor onder meer encryptie. Waar de generator op oudere platforms nog afhankelijk was van willekeurige data, bijvoorbeeld afkomstig van muisbewegingen of toetsaanslagen, produceert de nieuwe generator zijn willekeurige data puur op basis van digitale input. Daarmee voldoet de drng aan diverse standaarden en is deze sneller dan de analoge versie.

Ook de zogeheten Security Mode Execution Prevention-technologie, of SMEP, is nieuw voor Ivy Bridge. Deze techniek moet voorkomen dat malware schade aanricht aan het besturingssysteem door escalaties van rechten te misbruiken.

Energiebeheer en overklokken

Fabrikanten kunnen het energiebeheer van de Ivy Bridge-processors exploiteren; de tdp van de processors is variabel en kan binnen zekere marges door oem's of odm's worden bepaald. De chips kunnen voor mobiel gebruik bovendien overweg met de low power-variant van ddr3-geheugen en energiezuinige processors kunnen daarnaast de System Agent met lagere spanningen aansturen. De variabele tdp kan ook worden uitgebuit bij laptops; de chips kunnen met een lagere tdp worden geconfigureerd voor mobiel gebruik, maar eenmaal gedockt of op het lichtnet aangesloten, kan de tdp dynamisch verhoogd worden.

/i/1316957831.png?f=imagenormal)

Een handig trucje dat bij Ivy Bridge wordt geïntroduceerd is Power Aware Interrupt Routing, kortweg PAIR. Als er energie bespaard moet worden, kan een slapende core dankzij deze techniek in een zuinige slaapstand blijven; PAIR stuurt dan een interrupt naar een core die al actief is. Wanneer echter maximale prestaties gewenst zijn, kan PAIR de interrupts juist verdelen, zodat niet gewacht hoeft te worden tot een core weer beschikbaar is. Een slapende core wordt in dat geval geactiveerd.

Voor het eenvoudig overklokken van de processors door de multipliers te verhogen werd in Ivy Bridge de maximale multiplier aangepast. Deze kan van 57x in Sandy Bridge naar 63x in Ivy Bridge worden ingesteld. Met een baseclock van 100MHz betekent dat een theoretische maximumsnelheid van 6,3GHz. Bovendien is de multiplier zonder tussentijdse reboots aan te passen.

Ook het overklokken van geheugen wordt uitgebreid. De maximaal ondersteunde snelheid komt op 2800 in plaats van 2133MHz te liggen. Bovendien is de geheugensnelheid in Ivy Bridge niet langer via een vaste divider afhankelijk van de cpu-kloksnelheid, maar kan de snelheid in stapjes van 200MHz worden aangepast.

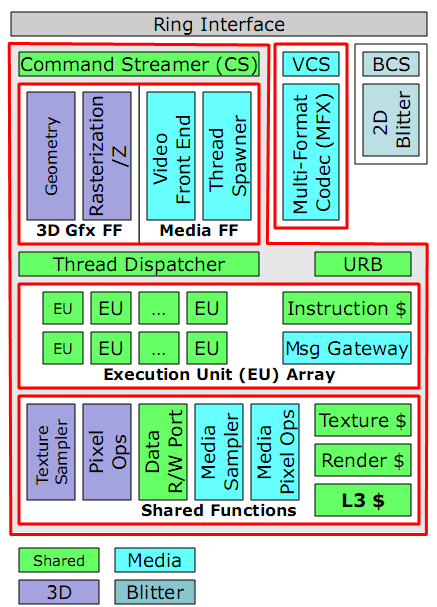

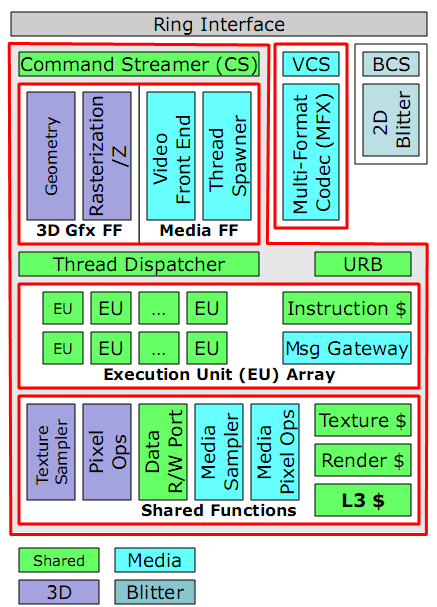

De gpu

Intel heeft de grootste veranderingen in Ivy Bridge gereserveerd voor de gpu. De fabrikant heeft zich ten doel gesteld om de grafische prestaties van zijn processors drastisch te verbeteren en zette daarin met Sandy Bridge een flinke stap vooruit. De voorgaande geïntegreerde grafische processors, zoals die in de Atom- en Clarkdale-processors, lieten flink te wensen over en waren niet geschikt voor gaming. Met de integratie van de gpu- en de cpu-cores in een enkele die in Sandy Bridge werden de prestaties aanzienlijk verbeterd, maar meer dan casual gaming zat er niet in. Met Ivy Bridge moeten de prestaties opnieuw een flinke stap voorwaarts maken en zouden de geïntegreerde gpu's een spelletje soepeler op het scherm kunnen vertonen.

De belangrijste vernieuwingen in Ivy Bridge zijn daarbij een meer schaalbare samenstelling van de gpu, ondersteuning voor DirectX 11 en de mogelijkheid om niet twee, maar drie displays aan te sturen. Over de dx11-functionaliteit moeten echter niet te veel illusies worden gemaakt. Een dx11-game met functies als tesselation ingeschakeld zal geen speelbare framerates halen.

De microarchitectuur van de gpu is op de schop genomen. De geometrie-front-end is aangepakt en is één van de vijf domeinen van de processor graphics. De overige domeinen zijn de slice common, met onder meer level 3-cache en rasterizer, de slice, met daarin de shader-units en samplers, het codex- en mediadomein, en ten slotte het displaydomein. Dat moet leiden tot meer schaalbaarheid met à la carte-onderdelen voor de gpu.

De Ivy Bridge-gpu komt in twee varianten, de GT1 met een vooralsnog onbekend aantal execution units of eu's en één texture sampler, en de GT2, met 16 eu's en twee texture samplers. Hoewel de toename in eu's vergeleken met Sandy Bridge gering is (die had er zes en twaalf), zijn de eu's van Ivy Bridge efficiënter. De eu's zouden ruwweg tweemaal zo veel operaties kunnen verwerken als die van Sandy Bridge, wat bijna resulteert in een verdubbeling van het aantal gigaflops dat de gpu kan leveren.

De toevoeging van een voor de gpu dedicated stuk level 3-cache leidt eveneens tot betere prestaties en bespaart bovendien energie. De ring-architectuur hoeft dan minder vaak gebruikt te worden om de met de cores gedeelde cache te benaderen. Ten slotte werd ook Intels Quick Sync-technologie verbeterd en kreeg de Ivy Bridge-gpu ondersteuning voor resoluties tot 4096 bij 4096 pixels, ofwel 4K-schermen.

Chipsets en processors

Het moge duidelijk zijn: met Ivy Bridge voert Intel een flink aantal verbeteringen door ten opzichte van de Sandy Bridge-generatie Core-processors. Met zijn 1,4 miljard transistors vormt Ivy Bridge vooral voor mobiele toepassingen een interessante chip. Het energiebeheer is sterk verbeterd en de prestaties zouden daar nauwelijks onder lijden.

Het goede nieuws voor desktopbezitters die eerder dit jaar in een Series 6-moederbord investeerden, is dat de Ivy Bridge-socket compatibel is met die moederborden. De nieuwe generatie processors kan dus gewoon in een P67-, H67- of Z68-moederbord worden gestoken. Alleen ontbreekt dan native usb 3.0-support.

| Chipset | Z77 | Z75 | H77 |

| Socket |

lga1155 |

lga1155 |

lga1155 |

| Srt |

Ja |

Nee |

Ja |

| Usb-poorten (totaal/usb 3.0) |

14 (4) |

14 (4) |

14 (4) |

| Sata-poorten (totaal/sata-600) |

6 (2) |

6 (2) |

6 (2) |

| Pci-express-poorten |

x16 of 2x x8 of 1x x8 + 2x x4 |

1x x16 of 2x x8 |

1x x16 |

| Overklokondersteuning |

Ja |

Ja |

Nee |

| Gpu-ondersteuning |

Ja |

Ja |

Ja |

In de nieuwe chipset-serie voor Ivy Bridge, de Series 7-chipset voor dito moederborden, is standaard wel usb 3.0-support aanwezig. De ssd-caching-techniek, die Intel met Z68 introduceerde, de Smart Response Technology, wordt in de 7-serie eveneens gehandhaafd. Ook zijn de pci-express-lanes van Ivy Bridge van de derde generatie, wat de bandbreedte verdubbelt ten opzichte van pci-express 2.0.

De belangrijkste chipsets voor Ivy Bridge, Z77, Z75, H77, Q77 en Q75, zijn voor zakelijk gebruik en B75 is een uitgeklede versie. Met Z77 en Z75 kan worden overgeklokt; Z75 ondersteunt als enige bord geen srt. De borden hebben zes sata-poorten, waarvan twee sata-600-poorten. Van de veertien usb-poorten zijn er vier met de usb 3.0-standaard uitgerust.

Op de configuraties van de processors moet nog gewacht worden tot Intel de Ivy Bridge-serie introduceert. Wanneer dat precies gebeurt, is onbekend, maar het zou ergens in de eerste helft van 2012 zijn.

/i/1316954865.png?f=imagenormal)

/i/1316954936.png?f=imagenormal)

/i/1316955077.png?f=imagenormal)

/i/1316957831.png?f=imagenormal)

/i/1334765845.png?f=fpa_thumb)

/i/1334763853.png?f=fpa_thumb)

/i/1294416060.png?f=fpa)

/i/1315951086.png?f=fpa)

/i/1306834994.png?f=fpa)

:strip_exif()/i/1307452229.jpeg?f=fpa)

/i/1242207182.png?f=fpa)

/i/1304531796.png?f=fpa)

/i/1247579454.png?f=fpa)