Intel zou met een project bezig zijn om het statische geheugen in processors te vervangen door dynamisch geheugen. Dram is compacter en goedkoper en de bandbreedte zou verveelvoudigen.

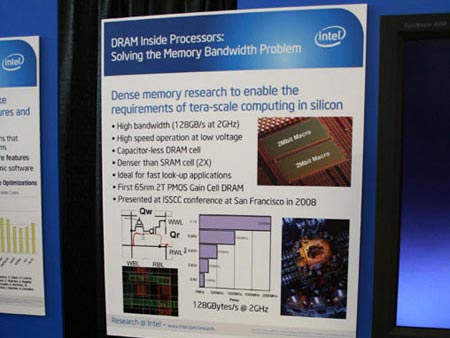

Een onderzoeksgroep van Intel toonde tijdens de Research@Intel Day een volgens hen veelbelovende ontwikkeling: in cpu's zou sram door dram vervangen kunnen worden. De caches in processors bestaan traditioneel uit statisch ram, met als voornaamste beweegredenen de hogere snelheden en lagere energiebehoefte ten opzichte van dynamisch ram. Sram is echter ook duurder dan dram en heeft relatief veel transistors, en dus ruimte, voor een enkel bit nodig. De onderzoekers van Intel zijn er nu echter in geslaagd om dram te construeren dat uit slechts twee transistors bestaat en geen condensators nodig heeft.

Het Intel-team zegt in staat te zijn om het compacte dram op snelheden tot 2GHz te klokken wanneer een 65nm-productieproces gebruikt wordt. Het 2T-dram, zoals het compacte geheugen gedoopt is, zou daarmee snelheden van 128GBps tussen de cores van de processor mogelijk maken. Ter vergelijking: de Harpertown-core van nieuwe Xeons beschikken over een bandbreedte van 18 tot 20GBps. Wanneer de snelheid van het dram verder omhoog geschroefd wordt om in de pas te lopen met Intels snelste quadcores, die op 3,2GHz tikken, zou de bandbreedte zelfs tot ruim 200GBps kunnen stijgen, tien keer zo snel als in de Xeons. Dat zou volgens Intel mogelijk zijn als het 2T-dram op 45nm wordt geproduceerd. De techniek zal mogelijk voor het eerst in de opvolger van de Larrabee-core gebruikt worden.

/i/1260965273.png?f=fpa)

/i/1253695573.png?f=fpa)

/i/1151398892.png?f=fpa)

/i/1217843384.png?f=fpa)

/i/1204897246.png?f=fpa)