Onderzoekers van Intel en ST Microelectronics hebben voor het eerst phase change-geheugen gedemonstreerd waarbij per cel vier in plaats van twee fysieke 'states' ingezet kunnen worden om data op te slaan.

De bedrijven hebben hun vinding geopenbaard op de International Solid State Circuits Conference, die momenteel in San Francisco gehouden wordt. Intel en ST Microelectronics werken al tijden samen aan de ontwikkeling van phase change-geheugen en

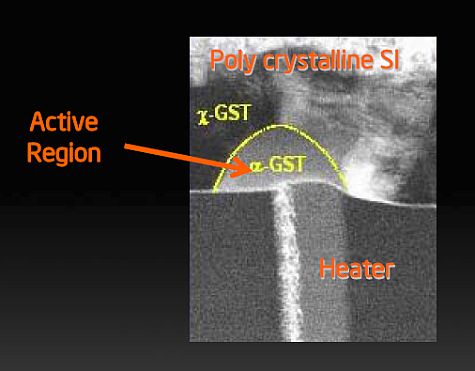

Intel en ST Microelectronics hebben nu bekendgemaakt dat het door hen gebruikte materiaal, dat ze GST gedoopt hebben, nog twee fysieke toestanden naast kristallijn en amorf kent, die bruikbaar zijn voor het opslaan van bits. Ook deze twee states kunnen bereikt worden door middel van gecontroleerde verhitting van het materiaal. De geheugencellen zijn vervolgens weer uit te lezen door de elektrische weerstand te meten; die waarde is namelijk afhankelijk van de toestand van het chalcogenide. De bedrijven konden zo multi-level pram-chips met een capaciteit van 256Mbit construeren. De snelheid waarmee de bits te schrijven zijn, is 'commercieel bruikbaar', zei Justin Rattner, cto van Intel, tijdens een conference call die aan de Issc-conferentie voorafging.

/i/1284994179.png?f=fpa)

/i/1272440032.png?f=fpa)

/i/1242207182.png?f=fpa)

:strip_exif()/i/1207063379.gif?f=fpa)