Innovative Sillicon heeft de tweede generatie van zijn zram-techniek aangekondigd. AMD - dat eerder een licentie op de eerste generatie nam - is weer de eerste en voornaamste klant. De nieuwe versie verbetert zowel de snelheid als de zuinigheid.

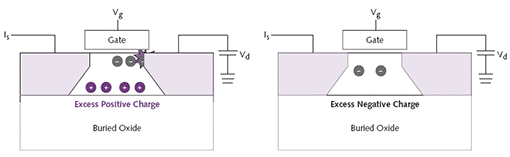

Zram heeft slechts één transistor per bit nodig, tegenover vijf à zes voor het sram-geheugen waar het cache van processors normaal van wordt gemaakt. Om dit voor elkaar te krijgen wordt slim gebruikgemaakt van de eigenschappen van de soi-wafers die onder andere door AMD en IBM gebruikt worden. Er kan meer dan 5Mbit (610KB) zram per vierkante millimeter gebakken worden met behulp van 65nm-techniek, wat nog eens verdubbeld kan worden met 45nm-transistors. AMD noemt het een 'extreem aantrekkelijke optie voor onze toekomstige processors', maar heeft vooralsnog geen definitieve toezeggingen gedaan over het gebruik ervan.

Het voornaamste probleem met zram zijn de prestaties. Omdat men vertrouwt op een subtiel effect in het silicium onderlaagje heeft men niet alleen weinig transistors en stroom nodig, maar moet men ook voorzichtig zijn bij het lezen en schrijven. De eerste generatie was om die reden niet sneller dan 200MHz. De nieuwe versie kan al een stuk sneller zijn: men beweert dat meer dan 400MHz mogelijk is. Door een soort ddr-opstelling te bouwen zou men zelfs boven de 1GHz uit kunnen komen. Dit is echter nog steeds maar een fractie van de snelheid van de processor zelf, waardoor zram eigenlijk afgeschreven kan worden als optie voor L1- of L2-cache, omdat het te veel vertraging zou opleveren en/of bandbreedte tekort komt. De meest waarschijnlijk plaats waar de techniek zijn debuut zal maken is in het L3-

/i/1204897246.png?f=fpa)