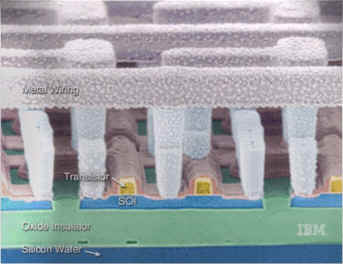

Bij EETimes valt te lezen dat AMD een licentie heeft verworven voor het gebruik van Z-ram, ook wel bekend als 'zero capacitor'-geheugen. Z-ram zou dankzij SOI-technologie een veel grotere dichtheid van componenten kunnen hebben, en daarmee is het heel geschikt om een veel grotere cache aan een processor te knopen dan wat momenteel haalbaar en betaalbaar is. Craig Sander, AMD-directeur met technologie in zijn portefeuille, wist te melden dat de chipfabrikant druk bezig is om te evalueren of de nieuwe techniek geschikt gemaakt kan worden voor de producten van het bedrijf, door tests uit te voeren met 90nm- en 65nm-transistors. Een concrete tijdlijn voor de productie van processors met Z-ram-caches kon hij nog niet geven, maar als de experimenten succesvol zijn zal de techniek zo snel mogelijk worden ingezet.

Hoewel de AMD-voorman nog de nodige slagen om de arm houdt als het om schaalbaarheid gaat, hoopt AMDzone dat de naar schatting vijfmaal grotere dichtheid van Z-ram ook vijfmaal grotere cachegeheugens betekent. Omdat een periode van twee jaar voor de overgang van plan naar productie gangbaar zou zijn, verwacht deze site dat we mogelijk eind volgend jaar al de eerste dualcore AMD's met in totaal 10MB aan L2-cache in de winkel zouden kunnen aantreffen, maar dat is wellicht wishful thinking. Dat deze techniek AMD mogelijk een voorsprong kan geven op de concurrentie is in ieder geval duidelijk. Z-ram is weliswaar ook voor andere producten van de chipfabrikant bruikbaar, maar dat zou vooralsnog te veel aanpassingen aan de productiefaciliteiten vergen. Wel werkt AMD op diverse terreinen nauw samen met IBM, maar of en hoe dat bedrijf met Z-ram aan de slag kan, is nog in nevelen gehuld.

Hoewel de AMD-voorman nog de nodige slagen om de arm houdt als het om schaalbaarheid gaat, hoopt AMDzone dat de naar schatting vijfmaal grotere dichtheid van Z-ram ook vijfmaal grotere cachegeheugens betekent. Omdat een periode van twee jaar voor de overgang van plan naar productie gangbaar zou zijn, verwacht deze site dat we mogelijk eind volgend jaar al de eerste dualcore AMD's met in totaal 10MB aan L2-cache in de winkel zouden kunnen aantreffen, maar dat is wellicht wishful thinking. Dat deze techniek AMD mogelijk een voorsprong kan geven op de concurrentie is in ieder geval duidelijk. Z-ram is weliswaar ook voor andere producten van de chipfabrikant bruikbaar, maar dat zou vooralsnog te veel aanpassingen aan de productiefaciliteiten vergen. Wel werkt AMD op diverse terreinen nauw samen met IBM, maar of en hoe dat bedrijf met Z-ram aan de slag kan, is nog in nevelen gehuld.