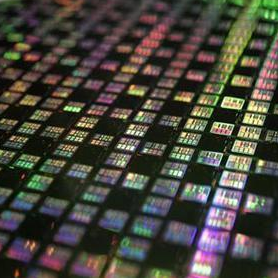

TSMC en Samsung hebben naar verluidt te maken met tegenvallende yields bij het produceren van 10nm-chips. Hierdoor zouden producten die in het eerste kwartaal van 2017 met chips op 10nm-formaat zouden verschijnen vertraging op kunnen lopen.

Volgens bronnen van DigiTimes heeft TSMC bestellingen lopen van merken als Apple, HiSilicon en MediaTek. Apple zou naar verluidt in maart 2017 met nieuwe iPads willen komen, maar deze zouden door de lage opbrengsten vertraagd kunnen worden. De bronnen geven verder aan dat in het tweede kwartaal van 2017 de eerste chips voor de volgende iPhone geproduceerd worden.

Volgens bronnen van DigiTimes heeft TSMC bestellingen lopen van merken als Apple, HiSilicon en MediaTek. Apple zou naar verluidt in maart 2017 met nieuwe iPads willen komen, maar deze zouden door de lage opbrengsten vertraagd kunnen worden. De bronnen geven verder aan dat in het tweede kwartaal van 2017 de eerste chips voor de volgende iPhone geproduceerd worden.

Ook Samsungs chipfabriek lijkt last te hebben van tegenvallende opbrengsten op het 10nm-procedé. Dit zou ertoe geleid hebben dat Qualcomm zijn plannen voor 2017 moest bijstellen. Het bedrijf was aanvankelijk van plan om meerdere socs op 10nm te laten produceren, maar houdt het nu naar verluidt alleen bij het aanstaande topmodel, de Snapdragon 835. Goedkopere chips, zoals de Snapdragon 660-serie, zouden op 14nm-formaat worden geproduceerd. Samsung kondigde in oktober aan dat het is begonnen met de productie van 10nm-chips.

TSMC had vorig jaar aangekondigd dat de eerste 10nm-chips vanaf eind 2016 beschikbaar zouden zijn. Volgens het bedrijf zou het kleinere formaat een prestatiewinst van 15 procent moeten opleveren bij hetzelfde verbruik of bij dezelfde prestaties een verbruiksafname van 35 procent.

Intel heeft ook moeite met het perfectioneren van het 10nm-proces. In 2015 maakte het bedrijf bekend dat het af zou stappen van de gebruikelijke 'tick-tock'-generaties, waarbij de ene generatie een nieuwe architectuur introduceerde en de opvolgende generatie de architectuur op een kleiner formaat werd geproduceerd. Als resultaat hiervan is de nieuwe Kaby Lake-generatie de derde op een rij die op 14nm wordt gebakken. Volgens experts is er in de praktijk weinig verschil tussen het 14nm-procedé van Intel en het 10nm-procedé van andere fabrikanten. De eerste 10nm-chips van Intel moeten in de tweede helft van 2017 verschijnen.

:strip_icc():strip_exif()/i/2001385603.jpeg?f=fpa_thumb)

:strip_exif()/i/1266478063.jpeg?f=fpa)

/i/1240844012.png?f=fpa)

/i/1297427597.png?f=fpa)

/i/2001331269.png?f=fpa)

/i/1304670251.png?f=fpa)

/i/1349425400.png?f=fpa)

:strip_exif()/i/1257241493.gif?f=fpa)