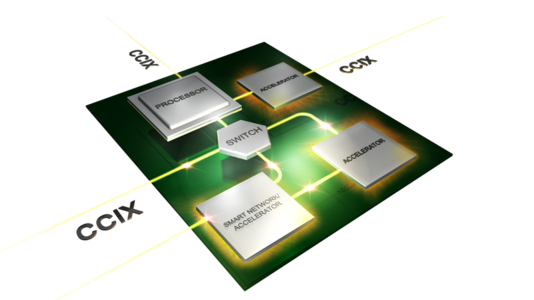

AMD, ARM, Huawei, IBM, Mellanox, Qualcomm en Xilinx hebben zich ten doel gesteld een nieuwe interconnect te ontwikkelen. De Cache Coherent Interconnect for Accelerators moet processors en accelerators van de verschillende fabrikanten aan elkaar knopen.

De Cache Coherent Interconnect for Accelerators of CCIX moet hardwareversnellers toegang tot data geven 'waar deze zich ook in het systeem bevindt', volgens de bedrijven. Het samenwerkingsverband claimt dat hardwareversnelling bij applicaties in datacentra een noodzaak is geworden in verband met voordelen op gebied van verbruik en omvang van componenten. Onder andere bij analyse van big data, machine learning en databasetoepassingen in het geheugen kunnen accelerators voor flinke snelheidswinst zorgen.

Google maakte vorig week bijvoorbeeld bekend zijn eigen Tensor Processing Units ontwikkeld te hebben. Het probleem is dat componenten van verschillende instruction set architectures niet op een consistente manier dezelfde geheugenpool kunnen aanspreken.

Details over de komende interconnect zijn er nog niet, maar de bedrijven streven naar een standaard die voor hogere bandbreedte, lagere latency en ondersteuning voor cache coherence zorgt. De specificatie moet zorgen dat processors op basis van verschillende architecturen eenvoudig data met accelerators als gpu's en fpga's kunnen delen. Er bestaan al enkele standaarden van specifieke fabrikanten voor het delen van geheugen, zoals IBM's coherent processor accelerator interface en Nvidia's NVLink, maar er is nog geen open universele interconnect.

Intel staat niet in de rij van fabrikanten die aan ccix werken. De marktleider voor datacenterchips heeft zijn eigen OmniPath-interconnect en nam vorig jaar de fpga-fabrikant Altera over, wat mogelijk de reden is dat de concurrenten zijn gaan samenwerken.

/i/2002553386.png?f=fpa)

/i/1309767168.png?f=fpa)

/i/1242207182.png?f=fpa)

/i/1290681265.png?f=fpa)

/i/1160648189.png?f=fpa)

/i/1340056824.png?f=fpa)