Toshiba en IBM zijn er in geslaagd om twee verschillende wafers met elkaar te verbinden, waardoor de mobiliteit van elektronen en elektronengaten kan worden vergroot. Dat zou betere field effect transistors opleveren.

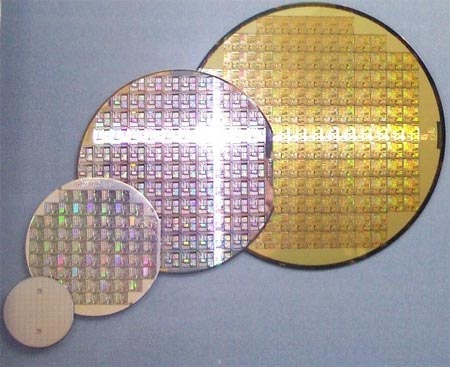

Eén van de mogelijkheden om de snelheid van cmos-chips te verhogen, is de communicatie tussen transistors te vergemakkelijken. De mobiliteit van elektronen en de bijbehorende elektronengaten speelt hierbij een belangrijke rol. Een van de belangrijkste eigenschappen van een wafer is in dat verband de oriëntatie van de gebruikte silliciumkristallen. De onderzoekers van Toshiba en IBM zijn er nu in geslaagd om wafers op basis van twee verschillende typen, die naar aanleiding van de kristaloriëntatie (100)wafers en (110)wafers worden genoemd, met elkaar te verbinden. De twee wafers werden daartoe 45 graden ten opzichte van elkaar gedraaid en verbonden met een dunne dsb-laag.

De resulterende 'hybride' wafers leveren volgens de onderzoekers tien procent betere prestaties dan combinaties waarbij de rotatie niet wordt toegepast; de vooruitgang bedraagt zelfs dertig procent ten opzichte van standaard (100)wafers. Door gebruik te maken van hybride wafers kunnen positief geladen field effect transistors, of pfets, profiteren van het (110)substraat, terwijl negatief geladen fets beter gebaat zijn bij (100)substraten. De gemengde wafers zorgen voor beter presterende pfets, zonder dat er een nadelig effect op de prestaties van de nfets is.

:strip_exif()/i/1184619892.gif?f=fpa)