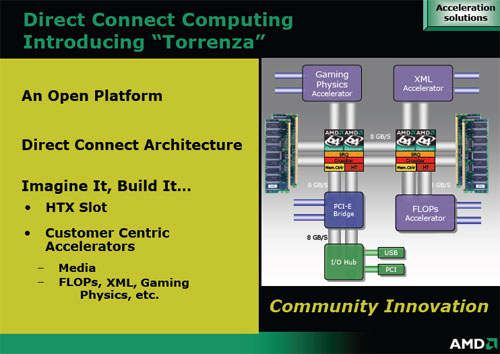

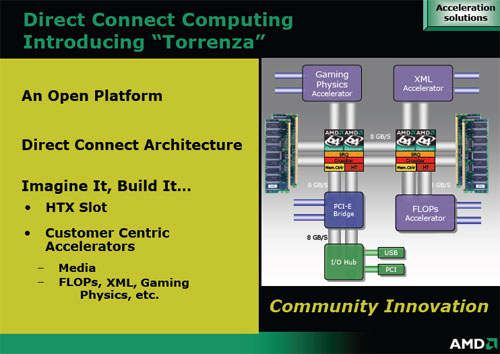

AMD heeft in het kader van zijn Torrenza-initiatief de specificaties van Socket F vrijgegeven. Dit stelt bedrijven in staat om producten te ontwikkelen die rechtstreeks op een Opteron-moederbord geprikt kunnen worden en naadloos met de processors kunnen communiceren via het HyperTransport-protocol. AMD denkt voor mogelijke toepassingen onder andere aan versnellers voor XML, physics, VoIP, Java en multimedia. Eén van de eerste gegadigden om de technologie te gebruiken is de supercomputerbouwer Cray, die plannen heeft om een herconfigureerbare chip (FPGA) rechtstreeks aan de Opteron te koppelen. Een FPGA kan geprogrammeerd worden om een specifiek algoritme vele malen sneller uit te voeren dan een voor algemeen gebruik bedoelde chip, wat onder andere voor wetenschappelijk onderzoek handig kan zijn. De rechtstreekse koppeling met HyperTransport zorgt ervoor dat er genoeg bandbreedte is om die kracht ook te kunnen benutten. Verder wordt het initiatief enthousiast ontvangen door de complete top vijf serverbouwers (IBM, HP, Sun, Dell en Fujitsu), waardoor het met de ondersteuning wel goed lijkt te zitten. Zolang bedrijven interessante toepassingen weten te verzinnen kunnen klanten daar dus van profiteren.

Deze zet kan echter grotere gevolgen hebben dan 'alleen maar' de ontwikkeling van strak geïntegreerde coprocessors. Volgens de geruchten zijn IBM en Sun namelijk bezig om hun respectievelijke serverarchitecturen - Power en UltraSparc - aan te passen zodat ze (ook?) op de Opteron-socket kunnen werken. Voor Intel moet het idee dat zijn drie belangrijkste concurrenten in de toekomst mogelijk een gezamenlijk platform krijgen een beangstigende gedachte zijn, maar tegen de tijd dat het echt zover is zal men wel een antwoord hebben in de vorm van CSI. Ook deze techniek staat in het kader van schaalbaarheid, consolidatie (in dit geval van Itanium en Xeon) en open specificaties. Of Intel ook bereid is om zijn socket te openbaren is echter nog niet duidelijk.