Ars Technica gaat vandaag verder waar het de vorige keer ophield. Na de geschiedenis van de eerste Pentium-architectuur tot en met de Pentium III werpt men in deel twee van dit overzicht een blik op de Pentium 4, de Pentium M en de Prescott. Toen de Pentium 4 voorgesteld werd, was er nogal scepsis omtrent het nieuwe ontwerp. De prestaties per klokcyclus vielen nogal tegen, en het compleet nieuwe ontwerp stuitte ook op de nodige kritiek. De pipeline van de P6-architectuur bestond uit twaalf stappen die voor de Pentium 4 opgesplitst werden naar twintig etappes. Doordat in elke fase minder gewerkt moet worden, kan de kloksnelheid omhoog, wat tot resultaat heeft dat hogere kloksnelheden zich ook vertalen in betere prestaties.

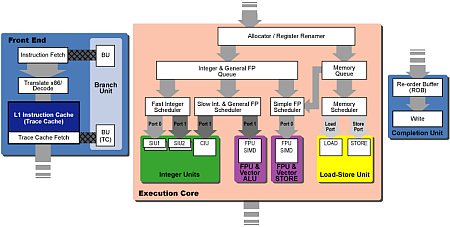

In de P6-architectuur werd reeds de buffer besproken die er voor zorgde dat eventuele haperingen in de aanvoer van instructies opgevangen werden zodat de uitvoerende hardware geen tijd hoeft te verliezen. Door de nog langere pipeline van de Pentium 4 was het reservation station echter niet meer voldoende. Door de hogere kloksnelheden kon de front end-hardware de instructies niet snel genoeg meer aanleveren. Een mogelijk oplossing was het uitbreiden van de buffer en het instruction window geweest. Hoewel dit een van de maatregelen is die Intel nam - de Pentium 4 kan maar liefst 126 instructies tegelijk in de gaten houden -, werd een andere belangrijke wijziging aangebracht. De trage x86-vertaalstap werd namelijk uit de pipeline verwijderd door de L1-cache om te vormen tot een cache voor gedecodeerde instructies.

De P6 haalde de x86-instructies uit de L1 cache en converteerde deze naar micro-operations (eenvoudige en uniforme interne instructies die gemakkelijker beheerd kunnen worden) voor ze naar het reservation station verplaatst werden. De nieuwe Pentium 4 daarentegen haalt de x86-instructies op uit het L2-cachegeheugen, vertaalt deze naar reeksen micro-operations en plaatst deze traces vervolgens in de nieuwe L1-cache. Hierdoor hoeven de instructies niet meer vertaald te worden in de pipeline en kunnen ze de weg naar de uitvoerende hardware sneller afleggen. Hoewel Intel geen details wou vrijgeven omtrent deze cache, beweert men dat er 12KB uops (micro-operations) in opgeslagen worden met een hit ratio equivalent aan dat van 16KB traditionele L1-cache. De trace cache is dus een reservoir waarin de vertaalde uops opgeslagen worden voordat ze naar het kleinere instructiereservoir verhuizen.

Het werd reeds eerder vermeld, maar ook het instruction window werd aangepast voor de Pentium 4. Zoals in het vorige artikel duidelijk gemaakt werd, bestond het instruction window van de P6 uit het reservation station en de reorder buffer. Ook de Pentium 4 beschikt over een reorder buffer die overigens heel wat groter is dan in de P6. Het reservation station werd voor de Pentium 4 echter opgesplitst in verschillende onderdelen. Per klokcyclus kunnen namelijk drie uops uit de trace cache naar de reorder buffer overgeheveld worden. Van daaruit worden de instructies in een van beide wachtrijen geplaatst: geheugenoperaties gaan in de memory queue terwijl rekenwerk in de arithmetic-logic queue geplaatst wordt.

Het werd reeds eerder vermeld, maar ook het instruction window werd aangepast voor de Pentium 4. Zoals in het vorige artikel duidelijk gemaakt werd, bestond het instruction window van de P6 uit het reservation station en de reorder buffer. Ook de Pentium 4 beschikt over een reorder buffer die overigens heel wat groter is dan in de P6. Het reservation station werd voor de Pentium 4 echter opgesplitst in verschillende onderdelen. Per klokcyclus kunnen namelijk drie uops uit de trace cache naar de reorder buffer overgeheveld worden. Van daaruit worden de instructies in een van beide wachtrijen geplaatst: geheugenoperaties gaan in de memory queue terwijl rekenwerk in de arithmetic-logic queue geplaatst wordt.

Deze wachtrijen hebben een FIFO-structuur en zijn gelinkt met verschillende schedulers. Deze bepalen wanneer de noodzakelijke bronnen en gegevens voor een instructie beschikbaar zijn en plannen op basis daarvan de volgorde waarin de uops uitgevoerd worden. Het voordeel van deze splitsing van het instruction window in twee wachtrijen is dat men de verzekering heeft dat beide types van instructies steeds beschikbaar zullen zijn, zodat een overvloed aan rekeninstructies bijvoorbeeld er niet voor zorgt dat geheugenbewerkingen blijven liggen. Het is dus de bedoeling dat, door al deze aanpassingen, de uitvoerende hardware een onafgebroken aanvoer van nieuwe opdrachten krijgt. Bij de P6 werden instructies uit het reservation station door een van de vijf beschikbare poorten naar de execution core gestuurd.

De Pentium 4 beschikt echter slechts over vier poorten: twee voor geheugenoperaties, twee voor alle andere instructies. Met deze vier poorten kan de Pentium 4 echter toch zes uops per klokcyclus naar de execution core sturen. Execution port 0 is verbonden met een Fast Integer ALU die integerberekeningen uitvoert, evenals logische bewerkingen. Deze ALU staat ook in voor het evalueren van branch-voorwaarden en uitvoeren van store-data uops. Doordat deze ALU zowel op de rijzende als op de dalende flank van een kloktik instructies kan uitvoeren werkt deze eenheid dubbel zo snel als de klokfrequentie. Naast de eerste ALU is execution port 0 ook verbonden met een eenheid die instaat voor het verplaatsen en opslaan van floating-point instructies en SSE-bewerkingen.

De Pentium 4 beschikt echter slechts over vier poorten: twee voor geheugenoperaties, twee voor alle andere instructies. Met deze vier poorten kan de Pentium 4 echter toch zes uops per klokcyclus naar de execution core sturen. Execution port 0 is verbonden met een Fast Integer ALU die integerberekeningen uitvoert, evenals logische bewerkingen. Deze ALU staat ook in voor het evalueren van branch-voorwaarden en uitvoeren van store-data uops. Doordat deze ALU zowel op de rijzende als op de dalende flank van een kloktik instructies kan uitvoeren werkt deze eenheid dubbel zo snel als de klokfrequentie. Naast de eerste ALU is execution port 0 ook verbonden met een eenheid die instaat voor het verplaatsen en opslaan van floating-point instructies en SSE-bewerkingen.

Execution port 1 is op zijn beurt verbonden met een tweede double-speed ALU, die echter enkel integerbewerkingen uitvoert. Daarnaast is er ook een trage integer ALU die de tragere bewerkingen zoals 'shift' en 'rotate', die niet in een halve klokcyclus uitgevoerd kunnen worden, voor zijn rekening neemt. De derde ALU waarmee deze port verbonden is, berekent floating-point en SSE-instructies, evenals MMX-bewerkingen. De eigenschap van de twee snelle ALU's om zowel op de rijzende als de dalende flank een integerbewerking uit te voeren, houdt in dat de Pentium 4 eigenlijk over vijf logische ALU's beschikt. Dit verklaart dan ook meteen waarom de Pentium 4 het in veel integer-benchmarks zo goed doet. Met de Pentium 4 werd overigens ook SSE 2 geïntroduceerd. Deze technologie bood niet alleen een 128-bits datatype met twee double-precision floating-point argumenten maar onder andere ook ondersteuning voor SIMD-berekeningen met 64-bits integers als argumenten en uitgebreide ondersteuning voor geheugenbewerkingen.

Deze uitbreidingen zijn overigens een illustratie van Intels strategie om kleinere transistoren niet enkel te benutten om de kloksnelheid omhoog te halen, maar om extra functies aan de core toe te voegen. De verbeterede SIMD-support biedt echter niet aan alle applicaties zoveel voordelen. De prestatieverbetering is afhankelijk van hoe sterk de software gebruikmaakt van specifieke hardware. Dit in tegenstelling tot een verbetering van hardware die, onafhankelijk van de software, een prestatieverbetering teweeg brengt. Zoals eerder al vermeld werd is een van de gevolgen van de lange pipeline en hoge kloksnelheid de noodzaak voor een groter instruction window. Een ander gevolg is echter de complexiteit van de hardware die instaat voor de branch prediction. Door de langere pipeline gaan bij een verkeerde voorspelling namelijk nog meer instructies verloren dan wat bij de P6 het geval was.

Daarom beschikt de Pentium 4 ook over twee branch predictors: een dynamische en een statische. De dynamische predictor bestaat uit een Branch History Table en een Branch Target Buffer. Codetakken die niet dynamisch voorspeld kunnen worden, doordat ze bijvoorbeeld niet in de BHT voorkomen, worden door de statische predictor afgehandeld. Deze gaat overigens relatief eenvoudig te werk en gaat uit van de veronderstelling dat een codetak meestal voorkomt als eindvoorwaarde in een loop. Voorwaartse takken worden daarom altijd voorspeld als 'zal niet genomen worden' terwijl takken in de code die terugkeren als 'zal genomen worden' voorspeld worden.

Daarom beschikt de Pentium 4 ook over twee branch predictors: een dynamische en een statische. De dynamische predictor bestaat uit een Branch History Table en een Branch Target Buffer. Codetakken die niet dynamisch voorspeld kunnen worden, doordat ze bijvoorbeeld niet in de BHT voorkomen, worden door de statische predictor afgehandeld. Deze gaat overigens relatief eenvoudig te werk en gaat uit van de veronderstelling dat een codetak meestal voorkomt als eindvoorwaarde in een loop. Voorwaartse takken worden daarom altijd voorspeld als 'zal niet genomen worden' terwijl takken in de code die terugkeren als 'zal genomen worden' voorspeld worden.

De pipeline van de Pentium 4 is overigens de eerste die gebruik maakte van drive stages. Deze stappen zorgen er alleen maar voor dat de kloksnelheid van de processor niet gelimiteerd wordt door de tijd die signalen nodig hebben om hun doel te bereiken. Verder hebben deze stappen echter geen enkel nut en vormen ze dan ook een van de nadelen van de hoge kloksnelheid. Dit is namelijk nog een extra stap in de pipeline die in het geval van een branch misprediction gewist moet worden. De pipeline van de Pentium 4 doet dus uiteindelijk hetzelfde als bij de P6, maar splitst bepaalde stappen op in meerdere onderdelen zodat de pipeline langer maar sneller wordt.

Het is reeds bij elke generatie Pentium-processors aan bod gekomen en ook bij de Pentium 4 wil men even stilstaan bij de x86-ondersteuning. Bij de Pentium 4 is dit echter een geval apart, aangezien de trace cache zowel een symptoom als een oplossing voor de x86-ondersteuning is. Omdat chips die geen ondersteuning voor x86 bieden ook een L1-cache hebben die vergelijkbaar is met de trace cache kan deze niet als een echte 'kost' aangerekend worden. Door zijn complexe eigenschappen, zoals de mogelijkheid om trace segments op te stellen, wordt hij echter ingewikkelder dan traditioneel L1-cachegeheugen, wat dan weer een argument is om de x86-ondersteuning wel als een nadeel te beschouwen.

Om het Pentium 4-verhaal af te sluiten wordt nog een kleine zijstap richting hyperthreading gemaakt. HT, of simultane multi-threading, maakt het mogelijk om verschillende threads tegelijk uit te voeren. Eenvoudig uitgelegd komt het erop neer dat het instruction window niet alleen langer geworden is, maar ook breder zodat instructies van twee verschillende threads bekeken kunnen worden. Voor een meer uitgebreide uitleg wordt echter naar een ander artikel verwezen. Iets meer dan een jaar geleden werd de Pentium M voorgesteld. Hoewel Intel weinig details heeft vrijgegeven over deze architectuur, zijn er toch enkele opvallende aanpassingen die de moeite van het vermelden waard zijn. Deze generatie is overigens gebaseerd op de Pentium III-architectuur met enkele aanpassingen die hem op de Pentium 4 doen lijken, maar niet zo ingrijpend zijn als bij de Pentium 4 het geval is.

Om het Pentium 4-verhaal af te sluiten wordt nog een kleine zijstap richting hyperthreading gemaakt. HT, of simultane multi-threading, maakt het mogelijk om verschillende threads tegelijk uit te voeren. Eenvoudig uitgelegd komt het erop neer dat het instruction window niet alleen langer geworden is, maar ook breder zodat instructies van twee verschillende threads bekeken kunnen worden. Voor een meer uitgebreide uitleg wordt echter naar een ander artikel verwezen. Iets meer dan een jaar geleden werd de Pentium M voorgesteld. Hoewel Intel weinig details heeft vrijgegeven over deze architectuur, zijn er toch enkele opvallende aanpassingen die de moeite van het vermelden waard zijn. Deze generatie is overigens gebaseerd op de Pentium III-architectuur met enkele aanpassingen die hem op de Pentium 4 doen lijken, maar niet zo ingrijpend zijn als bij de Pentium 4 het geval is.

De belangrijkste wijziging is het grotere instruction window. Zo zijn de reorder buffer en het reservation station uitgebreid en ook de andere buffers (zoals de memory reorder buffer) zijn vermoedelijk wat groter gemaakt. Deze uitbreiding was nodig omdat de Pentium M ook enkele stappen aan de pipeline toevoegde. Hoewel Intel details hieromtrent niet wil bekendmaken, wordt algemeen vermoed dat er drie of vier stappen aan de pipeline toegevoegd werden zodat de kloksnelheid omhoog kon. Ook de branch prediction werd verbeterd. Zo kan deze generatie ook indirecte takken in de code voorspellen en beschikt hij met een loop detector over betere dynamische voorspellingen. Verder worden uops in de Pentium M nog eens extra vertaald naar macro-instructies. Door bepaalde groepjes uops samen te voegen in een macro-instructie, nemen ze slechts één entry in de reorder buffer en het reservation station in. De verschillende uops worden echter wel nog steeds apart uitgevoerd.

Dit brengt ons bij de meest recente versie van de Pentium-processor. De 90nm Pentium 4 zoals hij door Ars Technica genoemd wordt, ofwel de Prescott. Net zoals bij de Pentium M is Intel niet zo gul met informatie, maar dat sluit niet uit dat er toch verschillende aanpassingen in de architectuur bekend zijn. Zo is bijvoorbeeld de pipeline weer iets langer geworden in vergelijking met de Pentium 4, vermoedelijk twee stappen. Wat in die twee stages precies gebeurt is niet bekend, maar Intel stelt dat ze toegevoegd werden om de kloksnelheid gemakkelijker op te kunnen schalen. Ook de integer ALU's werden enigszins aangepast. Zo kreeg een van beide units extra functionaliteit om shifts en rotates uit te voeren, zodat deze instructies nu ook dubbel zo snel uitgevoerd kunnen worden. Bovendien werd een dedicated integer multiplier toegevoegd, vermoedelijk aan de ALU die de complexe integerbewerkingen voor zijn rekening neemt.

De reorder buffer kan bij de Prescott nog steeds 126 entries bevatten, maar het instruction window is groter geworden. Dit betekent dat de schedulers die de floating-point en SIMD-instructies plannen uitgebreid zijn, net zoals de wachtrijen die de instructies aan deze schedules aanleveren. Om deze grotere pipeline en buffers steeds te voorzien van voldoende rekenvoer werd het L1-cachegeheugen uitgebreid van 8KB tot 16KB en beschikt de Prescott over 1MB L2-cache. Met dertien nieuwe instructies introduceert de Prescott bovendien SSE3 dat betere conversies van floating-point naar integer kan uitvoeren, evenals videocodering, complexe berekeningen en andere multimediacode. Tot slot werd ook de branch prediction verbeterd. Door loops te bestuderen slaagde men er namelijk in om vooral de statische predictor te verbeteren. Volgens Intel is er namelijk een relatie tussen de afstand van de tak naar de voorwaarde. Indien een codepad niet dynamisch voorspeld kan worden zal de statische predictor zich dan ook baseren op deze afstand om te voorspellen welke tak genomen zal worden.

:strip_exif()/i/1084221250.jpg?f=fpa)