Tijdens de ISSCC in San Fransisco heeft Intel een paper gepresenteerd waarin de Teraflops Research Chip (TRC) wordt gepresenteerd. Op 3,16GHz kan deze testchip meer dan één biljoen drijvendekommabewerkingen per seconde uitvoeren (oftewel teraflops) bij slechts 62W.

De TRC maakt onderdeel uit van Intels Tera-scale Computing Research Program, een poging om de huidige dual- en multicoreprocessors op te schalen naar ontwerpen met tien tot honderden cores die zuinig met energie omspringen. Het project moet een processor mogelijk maken die de teraflopgrens doorbreekt, zonder meer energie te verbruiken dan huidige processors.

De TRC bestaat uit 100 miljoen transistors die met behulp van een 65nm-proces in een 275mm² grote chip werden 'gegoten'. Op een frequentie van 3,16GHz heeft de testchip een spanning nodig van 0,95V. Na productie bleken hogere frequenties ook mogelijk, tenminste als de voedingsspanning werd verhoogd. Het maximale wat erin zat was 5,7GHz bij een voedingsspanning van 1,35V, goed voor tachtig procent betere prestaties (1,81 teraflops). Hier stond echter tegenover dat het verbruikte vermogen meer dan verviervoudigde naar 265W. Volgens het onderzoek is het dan ook veel interessanter om het aantal cores op de chip uit te breiden, dan de frequenties (en spanning) te verhogen.

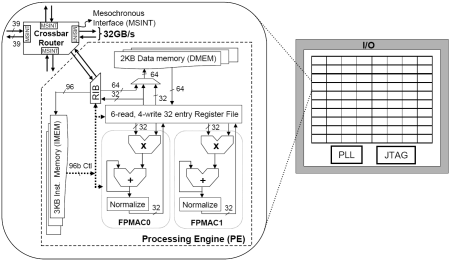

De TRC bestaat uit tachtig identieke tegels. Elke tegel heeft een processoreenheid (pe) en een router waarmee met de omliggende tegels kan worden gecommuniceerd. Elke pe bestaat uit twee onafhankelijke FPMAC's die elk twee floatingpointgetallen met elkaar kan vermenigvuldigen en optellen in een bewerking die negen kloktikken duurt. Verder heeft elke pe 3KB instructiegeheugen, 2KB datageheugen en 32 registers. De pe kan één 96-bit VLIW-instructies per kloktik decoderen, die tot acht verschillende bewerkingen kan beschrijven. Hierdoor kunner er elke kloktik twee FPMAC-bewerkingen, één load-, store-, sprong-, slaap-, packet-send- en packet-receive-bewerking worden uitgevoerd.

De router bestaat uit vijf poorten die 40bits breed zijn. Eén poort is met de pe verbonden en de overige vier poorten zijn met de omliggende tegels verbonden. Als de chip op een nominale frequentie van 4GHz werkt, zou elke router maar liefst 80GB per seconde aan gegevens kunnen verplaatsen. Deze communicatie gebeurt mesynchroon. Dat wil zeggen dat de klok van de onderdelen die met elkaar communiceren dezelfde frequentie hebben, maar niet dezelfde fase. Het voordeel hiervan is, dat er geen klokbuffers op de chip gebruikt hoeven te worden om ervoor te zorgen dat het kloksignaal aan de ene kant van de chip in fase is met het kloksignaal aan de andere kant van de chip. Hierdoor kan er energie bespaard worden.

Om nog meer energie te besparen is elke tegel opgesplitst in 21 verschillende zones die elk hun eigen kloksignaal hebben. Afhankelijk van of het onderdeel wel of niet gebruikt wordt, wordt dit kloksignaal automatisch aan- of uitgezet, een fenomeen dat 'fine grained clock gating' genoemd wordt. Als de klok van meerdere onderdelen in meerdere tegels tegelijkertijd wordt aangezet kan er echter stroompiek optreden die de goede werking van de chip kan beïnvloeden. Om dit te voorkomen hebben de ontwerpers een mechanisme ingebouwd waarmee elke FPMAC op de chip in zes stappen ontwaakt wordt.

Hoewel de grens van één teraflop met de TRC is doorbroken, betekent dit niet dat het project ten einde is. Zo willen de onderzoekers de TRC in de toekomst op een geheugenchip plakken, wat een razendsnelle communicatie met het geheugen mogelijk zou moeten maken. Daarnaast willen ze de TRC voorzien van cores die meer kunnen dan alleen het optellen en vermenigvuldigen van drijvendekommagetallen. De chips die in het kader van het project worden gemaakt zijn niet voor de verkoop bedoeld. De technieken en oplossingen daarentegen, die deze onderzoekschips mogelijk maken, zullen in de toekomst als basis dienen voor echte producten.

/i/1270729097.png?f=fpa)

/i/1256551756.png?f=fpa)

/i/1200408445.png?f=fpa)

:strip_exif()/i/1166195218.jpg?f=fpa)