Tilera introduceert vandaag de Tile64, een processor met 64 cores. Volgens het bedrijf liggen de prestaties van de cpu tien keer zo hoog als een Intel dualcore Xeon bij een lager energieverbruik.

De Tile64 is ontworpen voor embedded systemen zoals netwerkapparatuur en videostreamingservers. Tilera heeft naar eigen zeggen al een dozijn klanten, waaronder 3com en Toplayer, die de cpu in netwerk- en multimedia-apparatuur gaat integreren. 'We hebben deze architectuur ontworpen omdat bestaande multicore-technologieën maar schaalbaar zijn tot een handvol cores' , aldus Devesh Garg, topman van Tilera. Volgens het bedrijf vormen 64 cores nog maar het begin, de roadmap bevat plannen voor varianten met 36 cores en 120 cores en tegen 2014 zou met de technologie een chip met 1000 cores haalbaar zijn.

De Tile64 is ontworpen voor embedded systemen zoals netwerkapparatuur en videostreamingservers. Tilera heeft naar eigen zeggen al een dozijn klanten, waaronder 3com en Toplayer, die de cpu in netwerk- en multimedia-apparatuur gaat integreren. 'We hebben deze architectuur ontworpen omdat bestaande multicore-technologieën maar schaalbaar zijn tot een handvol cores' , aldus Devesh Garg, topman van Tilera. Volgens het bedrijf vormen 64 cores nog maar het begin, de roadmap bevat plannen voor varianten met 36 cores en 120 cores en tegen 2014 zou met de technologie een chip met 1000 cores haalbaar zijn.

Het startende bedrijf, opgericht in 2004, heeft de technologie gebaseerd op de mesh-architectuur van MIT-onderzoeker Anant Agarwal, die voor zijn RAW-project miljoenen dollars steun ontving van Darpa, het onderzoeksdepartement van de Amerikaanse defensie. Door de mesh-multicoretechnologie als uitgangspunt te nemen is Tilera naar eigen zeggen verantwoordelijk voor de eerste significante ontwikkeling op het gebied van chiparchitectuur in tien jaar.

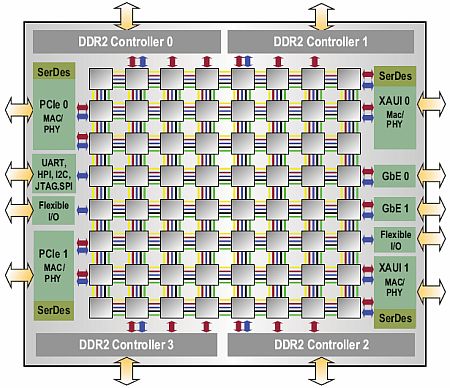

Het bijzondere van de Tile64 is dat deze geen bus bezit, maar dat deze vervangen is door een communicatieschakelaar op elke core. Door de processors in een grid op de chip te plaatsen, te vergelijken met de plattegrond van een moderne stad, ontstaat een efficiënt tweedimensionaal verkeerssysteem, aldus Tilera. Het bedrijf verwijst naar zijn grid-architectuur onder de noemer intelligent Mesh, of iMesh. De oplossing van het - toevallig? - 64 werknemers tellende bedrijfje lijkt op de 80-core prototype-cpu die Intel in februari van dit jaar onthulde.

Elk van de 64 kernen van de Tile64 is in staat zijn eigen besturingssysteem te draaien. Iedere core vormt bovendien een volledige, general-purpose processor die voorzien is van L1, L2 en gedistribueerde L3-cache. De cores maken onderdeel uit van een iMesh-netwerk, dat volgens het bedrijf zorgt voor snelle communicatie tussen de cores, het geheugen en de I/O.

Om kosten en energieverbruik zo laag mogelijk te houden bevat de Tile64 vier ddr2-geheugencontrollers en tal van I/O-interfaces zoals twee keer 10 Gbps XAUI, twee maal 10Gbps PCIe, twee keer 1Gbps Ethernet Rgmii en een programmeerbare I/O-interface voor ondersteuning van compactflash en diskdrives.

/i/1236852193.png?f=fpa)

/i/1287155856.png?f=fpa)

/i/1256551756.png?f=fpa)

:strip_exif()/i/1177326315.gif?f=fpa)