Inleiding: groter en goedkoper

Voor een beetje tweaker is het al jaren geen geheim, maar voor steeds meer gebruikers wordt het langzaam duidelijk: de beste upgrade voor je pc is een ssd. De snelheidswinst die ssd's bieden, maakt dat je desktop of laptop in het dagelijks gebruik veel rapper en responsiever aanvoelt. Niet meer wachten op het 'opspinnen', geen geluid van draaiende onderdelen, lagere gevoeligheid voor stoten en vallen: het zijn maar wat voordelen van een solid state drive boven een harde schijf.

/i/2001015091.jpeg?f=imagenormal)

Zo'n makkelijke keus was het echter niet altijd. In de begindagen van solid state drives voor consumenten, dus zogeheten drop-in replacements met sata-interface en 2,5"- of 3,5"-formfactor, waren de prijzen exorbitant hoog en de prestaties veelal niet bijzonder veel beter. Als voorbeeld nemen we de modellen uit de eerste ssd-review die Tweakers publiceerde: ssd-drives van Mtron en Memoright, die tegen de twintig euro per gigabyte kostten. Afgezien van de toegangstijden, die ook toen al een enorme verbetering ten opzichte van die van harde schijven boden, waren de prestaties niet eens zo geweldig. De sequentiële snelheden waren maar iets beter en in traces presteerden de drives twee tot vijf keer zo goed als harde schijven.

Inmiddels zijn ssd's zo'n tachtig keer zo goedkoop geworden en zijn de capaciteiten van 16GB tot 64GB gegroeid naar 120GB tot 2TB. De toegangstijden zijn nog steeds orden van grootte korter dan die van harde schijven en ook de sequentiële snelheden zijn inmiddels, mede dankzij nieuwe interfaces als pci-e, tientallen keren hoger dan die van hdd's. Ssd's zijn echter nog jong; waar harde schijven al minstens dertig jaar gemeengoed zijn, zijn ssd's dat nog geen tien jaar. Toch zijn ze al decennia lang in ontwikkeling, maar pas de laatste tien jaar zijn ze geschikt voor consumenten.

We kijken in dit achtergrondverhaal kort naar de geschiedenis van geheugen in het algemeen en ssd's in het bijzonder. We gaan in op de techniek die ten grondslag ligt aan nandgeheugen en hoe een ssd werkt, en ten slotte blikken we vooruit op de nabije toekomst.

Van vacuümbuis tot nand

Data is op veel verschillende manieren op te slaan en in de loop der jaren zijn diverse technieken ontwikkeld en weer ter ziele gegaan. We zullen niet alle geheugens de revue laten passeren, maar halen een korte selectie aan.

Een van de oudste vormen van geheugen is de vacuümbuis. Dergelijke buizen staan natuurlijk bekend als de voorloper van transistors, maar speciale vormen werden voor opslag gebruikt.

De eerste vorm van ram is waarschijnlijk een crt, of cathode ray tube. Jawel, eenzelfde buis als in twintigste-eeuwse tv's en monitors zat, werd net na de Tweede Wereldoorlog gebruikt als digitale opslag. Deze Williams-Kilburnbuis maakte gebruik van de kortstondige, residuele lading die op de fosforlaag van een crt achterblijft. Die lading werd gemeten met een metalen plaat voor de buis en zo konden bits opgeslagen worden. Echt betrouwbaar werkte dat niet en de techniek was geen lang leven beschoren.

De eerste vorm van ram is waarschijnlijk een crt, of cathode ray tube. Jawel, eenzelfde buis als in twintigste-eeuwse tv's en monitors zat, werd net na de Tweede Wereldoorlog gebruikt als digitale opslag. Deze Williams-Kilburnbuis maakte gebruik van de kortstondige, residuele lading die op de fosforlaag van een crt achterblijft. Die lading werd gemeten met een metalen plaat voor de buis en zo konden bits opgeslagen worden. Echt betrouwbaar werkte dat niet en de techniek was geen lang leven beschoren.

Een vacuümbuis die wat betrouwbaarder moest werken dan de Williams-Kilburnbuis was de Selectronbuis. Die was niet alleen handzamer, maar ook lastiger te bouwen en duur. Er is dan ook uiteindelijk slechts één computer met dergelijke buizen uitgerust. Beide buistechnieken moesten steeds ververst worden, omdat de lading geleidelijk verdween. In die zin zou je het dus kunnen vergelijken met dram.

/i/2001003657.jpeg?f=imagenormal) De buizentechnieken werden begin jaren vijftig opgevolgd door ringkerngeheugen, of magnetic-core memory. Hierbij werd data opgeslagen in kleine ringen die gemagnetiseerd konden worden door stroom te sturen door draden die rond de ringen werden gewonden. De polarisatie van het magneetveld gaf een 1 of 0 aan. Dat lijkt misschien een beetje op de techniek van harde schijven en het geheugen had geen spanning nodig om data vast te houden, maar ringkerngeheugen was tegelijk een vorm van ram, aangezien de data bij het uitlezen verloren ging. Ringkerngeheugen was een van de belangrijkste vormen van geheugen tussen 1955 en 1975.

De buizentechnieken werden begin jaren vijftig opgevolgd door ringkerngeheugen, of magnetic-core memory. Hierbij werd data opgeslagen in kleine ringen die gemagnetiseerd konden worden door stroom te sturen door draden die rond de ringen werden gewonden. De polarisatie van het magneetveld gaf een 1 of 0 aan. Dat lijkt misschien een beetje op de techniek van harde schijven en het geheugen had geen spanning nodig om data vast te houden, maar ringkerngeheugen was tegelijk een vorm van ram, aangezien de data bij het uitlezen verloren ging. Ringkerngeheugen was een van de belangrijkste vormen van geheugen tussen 1955 en 1975.

Om bij nand uit te komen, moeten we een uitstapje naar ram maken. Random-access memory werd in de jaren zestig ontwikkeld als snellere versie van shift-registers; die konden alleen sequentieel uitgelezen worden. Als opvolger van ringkerngeheugen kon ram, een transistortechniek met bipolaire transistors en flipflop-schakelingen, in willekeurige volgorde uitgelezen worden. Dat was nog een prijzige techniek, omdat per bit vier tot zes transistors nodig zijn. Dit type ram, ook wel statisch ram of sram genoemd, vinden we bijvoorbeeld nog terug als caches in processors. Het is het snelste, maar ook duurste type geheugen.

Een goedkoper ram is dram; de bits worden opgeslagen in de elektrische lading van een condensator en een enkele transistor doet dienst als schakelaar om de condensator te vullen of leeg te laten lopen. Lading in condensators opslaan heeft als nadeel dat de lading weglekt en dus ververst moet worden. Dit 'dynamische proces' leidt tot de naam dram, of dynamic ram: veel goedkoper om te maken en prima voor werkgeheugen.

Een goedkoper ram is dram; de bits worden opgeslagen in de elektrische lading van een condensator en een enkele transistor doet dienst als schakelaar om de condensator te vullen of leeg te laten lopen. Lading in condensators opslaan heeft als nadeel dat de lading weglekt en dus ververst moet worden. Dit 'dynamische proces' leidt tot de naam dram, of dynamic ram: veel goedkoper om te maken en prima voor werkgeheugen.

Waar in dram de bits in condensators worden opgeslagen, is dat bij rom niet nodig. Een transistor en een geleidend contact - of het ontbreken daarvan - maakt een 1 of een 0. Dat contact wordt tijdens het lithografische proces al gemaakt, dus veranderen kan niet. Het geheugen is alleen leesbaar en niet schrijfbaar, ofwel rom. Bij prom, of programmable rom, zijn de metalen contacten weg te smelten. Zo kun je het één keer programmeren.

/i/2001003763.png?f=imagenormal) Bij erasable prom, of eprom, werden voor het eerst transistors met een floating gate gebruikt. Die floating gate nam de taak van het metalen contact over en kon dus elektronisch beïnvloed worden. Het legen van de lading in de gate moest met uv-licht gebeuren door een karakteristiek venstertje in de chips en kon alleen voor de hele chip gedaan worden. Met de komst van eeprom kon het wissen met een elektrisch signaal plaatsvinden. Daar was een extra transistor voor nodig, wat het geheugen weer duurder maakte. Het grote voordeel is dat niet de hele chip gewist hoeft te worden, maar slechts een groep bytes.

Bij erasable prom, of eprom, werden voor het eerst transistors met een floating gate gebruikt. Die floating gate nam de taak van het metalen contact over en kon dus elektronisch beïnvloed worden. Het legen van de lading in de gate moest met uv-licht gebeuren door een karakteristiek venstertje in de chips en kon alleen voor de hele chip gedaan worden. Met de komst van eeprom kon het wissen met een elektrisch signaal plaatsvinden. Daar was een extra transistor voor nodig, wat het geheugen weer duurder maakte. Het grote voordeel is dat niet de hele chip gewist hoeft te worden, maar slechts een groep bytes.

We komen langzaamaan bij solid-state-opslag, want de volgende stap is het maken van flash-geheugen. Waar bij eeprom voor elke bit een extra transistor nodig was om de data te wissen, maakt flashgeheugen gebruik van een enkele 'wistransistor' om de hele chip te wissen. De kosten waren daardoor niet hoger dan die van eprom, maar je had wel het voordeel dat je data elektronisch kon wissen, in een 'flash'. Deze techniek werd in 1984 door Toshiba ontwikkeld en verfijnd om niet de hele chip, maar slechts delen te wissen. De data werd opgeslagen in de floating gates van transistors, die als norcellen waren gebouwd.

/i/1300351442.jpeg?f=imagenormal) In nandgeheugen ten slotte worden nand-gates gebruikt, maar (opnieuw) Toshiba bedacht een manier om de kosten verder te drukken. Door niet elke geheugencel individueel via een bit- en word-line aan te spreken, maar de word-lines door de verschillende cellen of bits te laten lopen, kon flink op de signaallijnen bespaard worden. De transistors staan dus in serie en per streng wordt een adreslijn gedeeld en hebben de cellen alleen individuele bitlijnen. Nandgeheugen wordt voor ssd's gebruikt en op de volgende pagina's bekijken we hoe nand werkt en welke verschillende typen nand er zijn.

In nandgeheugen ten slotte worden nand-gates gebruikt, maar (opnieuw) Toshiba bedacht een manier om de kosten verder te drukken. Door niet elke geheugencel individueel via een bit- en word-line aan te spreken, maar de word-lines door de verschillende cellen of bits te laten lopen, kon flink op de signaallijnen bespaard worden. De transistors staan dus in serie en per streng wordt een adreslijn gedeeld en hebben de cellen alleen individuele bitlijnen. Nandgeheugen wordt voor ssd's gebruikt en op de volgende pagina's bekijken we hoe nand werkt en welke verschillende typen nand er zijn.

Lezen en schrijven

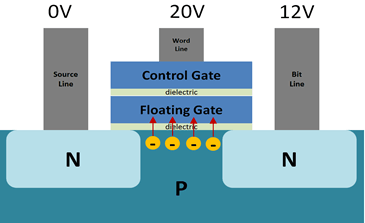

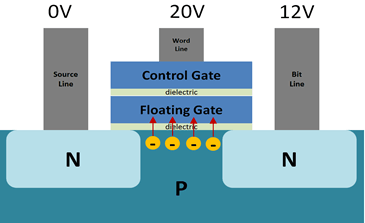

/i/2001003821.png?f=imagenormal) Elke afzonderlijke nor- en nandgeheugencel bestaat uit een transistor met niet één, maar twee gates: een control gate en een floating gate. Een dergelijke floating gate transistor, of fgt in het kort, slaat afzonderlijke bits op als lading in de floating gate. Door elektronen in de floating gate op te slaan, krijgt deze een negatieve lading, ofwel een logische 0. Om de geheugencel te wissen worden de elektronen uit de floating gate gestuurd, waardoor een logische 1 ontstaat.

Elke afzonderlijke nor- en nandgeheugencel bestaat uit een transistor met niet één, maar twee gates: een control gate en een floating gate. Een dergelijke floating gate transistor, of fgt in het kort, slaat afzonderlijke bits op als lading in de floating gate. Door elektronen in de floating gate op te slaan, krijgt deze een negatieve lading, ofwel een logische 0. Om de geheugencel te wissen worden de elektronen uit de floating gate gestuurd, waardoor een logische 1 ontstaat.

Nandgeheugen is een doorontwikkeling van norflash, met minder source- en bit-lines. De fgt's in een streng van gedeelde bit-lines worden samen een page genoemd en alle pages die een sourceline delen, worden een block genoemd. Lezen gaat per page en wissen gaat per block.

Dat levert wat uitdagingen voor lezen en schrijven op, omdat er meer ruis ontstaat. Bovendien is het geen echt random access-device meer, omdat niet elke bit afzonderlijk via een word- en bit-line kan worden aangesproken. In plaats daarvan wordt een volledige bit-line, met daaraan een hele string word-lines of afzonderlijke bits, uitgelezen. Alle word-lines van een page, zoals een dergelijke string genoemd wordt, worden actief geschakeld, behalve de te lezen word-line ofwel bit. Afhankelijk van de lading in de floating gate schakelt die fgt wel of juist niet en wordt op de bit-line een 0 of 1 gelezen. Omdat de te lezen bit ver van de bit-line kan liggen, treedt ruis bij het uitlezen op, wat kan resulteren in een verkeerd gelezen bit. Om dit tegen te gaan is ecc-technologie nodig.

/i/2001004439.png?f=imagenormal)

Deze bouw van nand maakt dat nandflash erg goedkoop te maken is, ondanks de noodzaak voor ecc-technologie. Er zijn minder transistors nodig dan bij norflash door het weglaten van veel source- en bit-lines en elke bit heeft maar één fgt nodig. Dat maakt nand echter niet langer een random device, omdat bits niet meer afzonderlijk uitgelezen kunnen worden. Seriële data kan daarentegen wel snel uitgelezen worden. Een ander probleem is de slijtage, door de manier waarop data geschreven en gelezen wordt.

Quantumeffecten voor schrijven

Er zijn een paar redenen waarom nandcellen slijten door program- en erase-cycli, kortweg p/e-cycli. De manier waarop nand beschreven wordt, is Fowler-Nordheim Tunneling, waarbij een hoog spanningsverschil tussen de source en drain enerzijds en de gate anderzijds wordt aangebracht, waardoor elektronen door het diëlektrum tunnelen en de floating gate negatief, of 0 maken. Om de cellen te wissen wordt opnieuw FN-tunneling gebruikt maar dan met een omgekeerd potentiaalverschil over de elektrodes. De spanningen voor schrijven en wissen zijn in de orde van grootte van 15-20V, wat direct verklaart waarom die acties tot schade leiden. Denk maar eens aan een processor die overgeklokt wordt; een spanningsverhoging van 1,3 naar 1,5V is al behoorlijk risicovol voor de transistors. Nandtransistors zijn weliswaar gemaakt voor die hoge spanningen, maar het leidt nog steeds tot schade.

Door de hoge spanningen en stromen heeft het halfgeleidermateriaal te lijden. Elektronen kunnen dan in het diëlektrum tussen het channel en de floating gate blijven steken en zo de geheugencel negatief houden. De elektronen kunnen dus niet langer uit de floating gate worden getunneld en de bit blijft een 0.

Door de hoge spanningen en stromen heeft het halfgeleidermateriaal te lijden. Elektronen kunnen dan in het diëlektrum tussen het channel en de floating gate blijven steken en zo de geheugencel negatief houden. De elektronen kunnen dus niet langer uit de floating gate worden getunneld en de bit blijft een 0.

Slc, mlc en tlc

In solid state drives wordt dus nand gebruikt om data in de vorm van bits op te slaan, zoals we op de vorige pagina zagen. Dit levert aanzienlijke kostenbesparingen op ten opzichte van andere non-volatiele opslagmethodes als norflash, omdat minder transistors per geheugencel nodig zijn. Voor massaopslag is meer altijd beter, dus fabrikanten zoeken naar meer manieren om de opslagcapaciteit te vergroten.

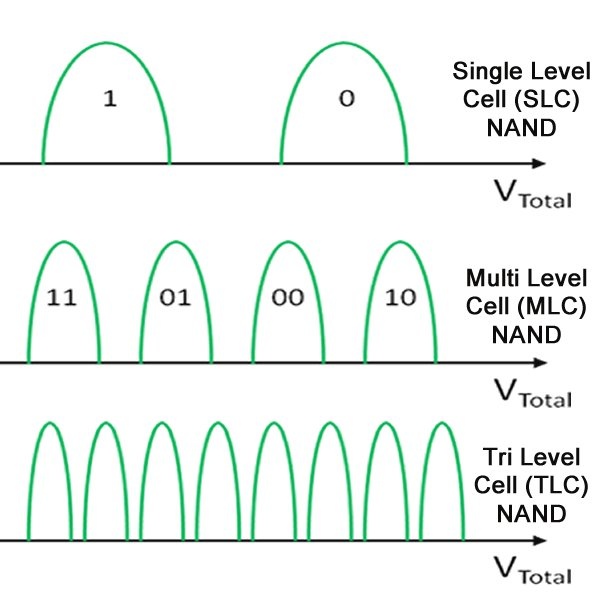

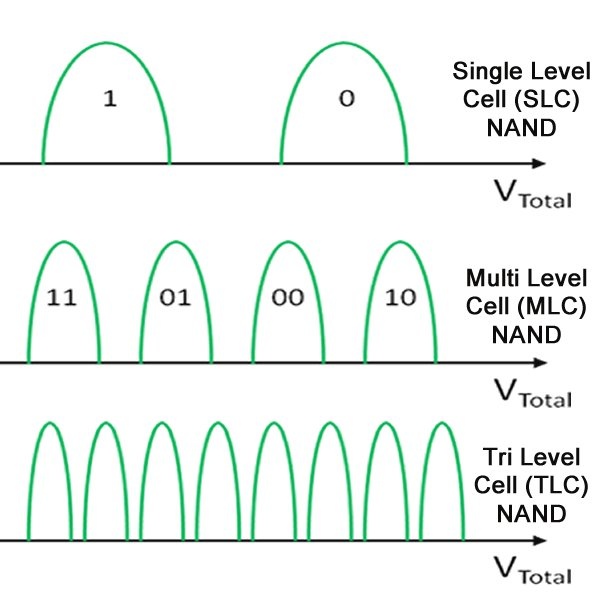

We kijken eerst naar de snelste, maar ook duurste vorm van nandgeheugen voor opslag: het slc-geheugen. Slc staat voor single level cell, ofwel een enkel niveau per cel. Dit type nand was het eerst ontwikkeld en elke bit heeft een geheugencel nodig, wat mede de oorzaak voor de hoge prijzen van vroege ssd's was. Tegenwoordig wordt slc-geheugen nog steeds gebruikt, onder meer voor ssd's die in servers worden ingezet.

/i/2001004465.png?f=imagenormal)

De s in slc is afkomstig van single en in slc-nand wordt dan ook een enkele bit per geheugencel opgeslagen. De eerder genoemde 0 en 1, die door veel of weinig elektronen in de floating gate te transporteren gerealiseerd worden, worden één-op-één vertaald in data. Daarom is slc lekker snel te lezen; er hoeft alleen gekeken te worden of de lading in de fgt hoog of laag is. Ook schrijven en wissen hebben niet enorm veel precisie nodig door het vrij makkelijk te detecteren ladingsverschil. Mede daarom heeft slc-geheugen een lange levensduur; de lekkende elektronen die tussen floating gate en channel terechtkomen, hebben niet zo snel invloed op de leesbaarheid van de bits.

Hoewel de bitdichtheid van nandflash al hoog is, bijna 1 bit per fgt, willen zowel fabrikanten als consumenten natuurlijk meer capaciteit voor lagere prijzen. Met mlc-geheugen wordt dit gerealiseerd. In plaats van 1 bit per fgt worden er twee opgeslagen. Dit maakt mlc wat trager met lezen en schrijven; de ladingsverschillen in de floating gates moeten een stuk preciezer worden. Zo worden veel elektronen, zeg 100 tot 75 procent van de capaciteit, in de gate als 00 gelezen. Als de gate voor 75 tot 50 procent 'gevuld' is, lezen we de waarde 01 uit, voor 50 tot 25 procent 10 en voor 25 tot 0 procent lezen we de twee bits als 11.

Door dit trucje verdubbelen fabrikanten dus in een keer de capaciteit van hun nand. De keerzijde is dat zowel lezen als schrijven zorgvuldiger, dus langzamer, moet plaatsvinden en de eerder genoemde ruis, en daarmee de noodzaak voor goede foutcorrectie, wordt groter. Een goede controller en dito ecc-techniek kunnen die nadelen goeddeels het hoofd bieden, reden voor bijna alle fabrikanten om slc-drives te laten vallen en mlc-drives voor consumenten te maken.

Eenzelfde truc als met mlc gedaan werd, kun je nog een keer doen, zodat je niet twee, maar drie bits per transistor kunt opslaan. Zo krijg je dus 000, 001, 010, 011, 011, 100, 101, 110 en 111 als bitwaardes. De ladingsverschillen in het resulterende tlc-geheugen zijn nog kleiner, maar als voordeel sla je weer twee keer meer data op in je flash. Ook nu geldt dat de kans op leesfouten groot is en de foutcorrectie nog harder aan de bak moet. Lezen en wissen duren dan ook zo'n drie keer zo lang als bij slc en schrijven gaat zelfs bijna vijf keer zo langzaam.

Waar slc-nand al problemen had met beperkte p/e-cycli door lekkende floating gates, kun je je voorstellen dat dat met mlc en helemaal met tlc nog erger is. De hoeveelheid elektronen die het verschil tussen opeenvolgende waardes maken, is dan steeds kleiner en een beetje lekkage kan tot gevolg hebben dat een andere waarde wordt uitgelezen dan opgeslagen werd. De levensduur van mlc- en nog sterker van tlc-nand wordt dus steeds korter.

Schaalproblemen

We zijn inmiddels dus van norflash overgegaan op nandflash met een hogere dichtheid per chip. Om nog meer bits op te slaan zijn we van slc- via mlc- naar tlc-nand gegaan, zodat we in elke transistor niet één, maar twee of drie bits kunnen opslaan. Om nog meer bits op een gegeven silicium oppervlak te kunnen opslaan, hebben fabrikanten nog een bekend trucje achter de hand: scaling.

Scaling wil niet meer zeggen dan simpelweg kleinere componenten op een chip maken, zodat er meer transistors per vierkante millimeter op passen en er dus meer bits opgeslagen kunnen worden. In processors wordt flink geschaald en fabrikanten hebben van 90nm en groter naar 65, 45, 32, 22 en inmiddels 14nm geschaald. Dat brengt voor processors voordelen als lager energieverbruik met zich mee, maar zogeheten lekstromen worden juist groter. Dat betekent dat lading in transistors kan lekken en de transistors zo ongewenst schakelen.

/i/2001004471.png?f=imagenormal)

Bij nandchips werkt scaling tot op zekere hoogte ook, maar sinds ongeveer 15 tot 19nm werkt dat niet zo goed meer. Nog erger dan bij transistors voor rekentaken, levert kleinere lithografie lekken op bij fgt's. Een bit houdt zijn waarde minder goed vast doordat er minder lading kan worden opgeslagen in de steeds kleiner wordende floating-gate-structuren. Ter illustratie: bij een transistorgrootte van ongeveer 30nm, de vorige generatie dus, bestaat een bit uit nog maar zo'n honderd elektronen. Afhankelijk van de nandtechniek blijft er nog maar een handjevol elektronen over om de bitwaarde vast te leggen; bij mlc-nand op 16nm zijn er slechts enkele tientallen elektronen per 'logic level' beschikbaar.

Bovendien heeft het lekken van elektronen door kwantumtunneling sneller een verandering van de waarde van de opgeslagen bits tot gevolg, zeker bij mlc- en tlc-nand. Daarnaast is er minder en dunner materiaal tussen de control gate en floating gate beschikbaar, waardoor het isolerende vermogen kleiner wordt en defecten door hoge spanningen bij wissen en programmeren relatief grotere gevolgen hebben. Kortom, kleinere transistors geven meer datadichtheid, maar het schalen is zeer lastig.

3d to the rescue

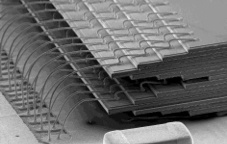

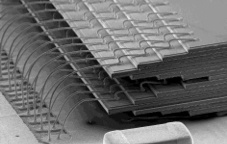

Een slimme oplossing voor het scalingprobleem is 3d-nand. Stel dat een enkele nandcel 60 bij 60nm meet; een streng van 64bit neemt dan een chipoppervlak van 480x480nm in beslag. Als je de lithografie naar 30x30nm per cel halveert, neemt diezelfde streng nog maar 240x240nm in beslag, een besparing van vier maal. Dat kun je echter niet blijven doen, maar wat wel kan, is de hoogte in. De nandstreng met 64 transistors wordt dan 'gebogen' tot een U-vorm, met 32 transistors aan beide poten. Dezelfde 64 transistors nemen dan nog maar 60x120nm in beslag op de chip, een enorme besparing die met lithografische scaling nooit gehaald kan worden. Zo kun je dus veel hogere dichtheden op je nandchip realiseren, zonder de nadelen van het gebruik van kleinere transistors.

/i/2001004495.gif?f=imagenormal)

Dat is precies wat nandfabrikanten gedaan hebben, maar het verschilt per fabrikant hoe ze dat precies implementeren. Samsung gebruikt een techniek die het Tanos, kort voor Tantalum-Alumina-Nitride-Oxide-Silicon, noemt. Voor de consument heeft het bedrijf dat eerst 3d-v-nand en later simpelweg v-nand genoemd. Het bedrijf maakt gebruik van charge-trap-technologie, waarbij siliciumnitride gebruikt wordt als charge trap voor de elektronen. Die vervangt de floating gate van gedoteerd polysilicium in plenair nand. Samsung maakt daarbij gebruik van een high-k-diëlektrum tussen de charge trap gate en de control gate, waarbij die laatste van tantalum wordt gemaakt.

Onder meer Toshiba/Sandisk maakt een iets simpelere 3d-variant, die niet van high-k-materialen en tantalum gebruikmaakt, maar van gedoteerd polysilicium. Dat maakt de constructie iets eenvoudiger, maar maakt nog steeds gebruik van siliciumnitride voor charge traps als floating gate. Deze techniek wordt gevat onder de noemer BiCS, kort voor Bit Cost Scaling, waarbij het schaalvoordeel uit het aantal lagen en niet uit een kleiner lithografieprocedé wordt gehaald. Intel/Micron maakt gebruik van een andere techniek, die niet met charge traps, maar met floating gates werkt. Dat zou de jarenlange ervaring met die techniek benutten, terwijl concurrenten met hun charge trap 3d-nand een nieuwere, onbekendere techniek moeten leren beheersen.

/i/2001004497.png?f=imagenormal)

Een lastig probleem bij de constructie van 3d-nand is de fabricage van de gaten door de lagen transistors. Een gat heeft een bepaalde aspectratio en dus een beperkte diepte. Hoe meer lagen een 3d-chip heeft, hoe groter het gat bovenin moet zijn; momenteel is een verhouding van ongeveer 60:1 de limiet. Door echter de lagen in verschillende stappen te bouwen, met voor elke stap een eigen stap voor het etsen van het gat, zouden fabrikanten lagen kunnen blijven stapelen en daarmee dus steeds hogere dichtheden van nand kunnen realiseren. Een andere lastige stap is het etsen van de structuren om de word-lines aan te sluiten. Daarvoor worden getrapte terrassen gemaakt die steeds op de word-line stoppen, waarop dan via's worden aangesloten. Ook deze stap wordt over het algemeen in verschillende ets-etappes uitgevoerd.

/i/2001004507.jpeg?f=imagenormal)

Het gebruik van charge traps in plaats van floating gates heeft een aantal voordelen, buiten scaling en dus goedkopere en grotere ssd's. De productie van charge traps is eenvoudiger, omdat ze niet 'gepatternd' hoeven te worden, maar in één lithografische stap in een chip gemaakt kunnen worden. Bovendien lekken ze niet zo makkelijk elektronen. Ook de spanning om ze te beschrijven is lager dan bij floating gates, wat de levensduur ten goede komt, nog los van de voordelen die een groter procedé biedt. Bovendien zou 3d-nand zowel zuiniger als sneller dan plenair nand zijn bij p/e-acties.

Verwar 3d-nand niet met gestapelde dies. Fabrikanten stapelen al jaren meer dan één die, plakjes silicium dus, op elkaar in een package. Een dergelijke package is de 'chip' die je op het printplaatje gesoldeerd ziet. Bij gestapelde dies worden de afzonderlijke siliciumchips via extreem dunne draadjes buitenlangs met elkaar en de bga-connector onderop verbonden. Er is een tussenvorm waarbij through silicon via's of tsv's gebruikt worden om een deel van de verbindingen te verzorgen. Bij 3d-nand gaan de transistors al in het silicium de hoogte in en bovendien kunnen afzonderlijke dies gestapeld worden binnen een package.

Verwar 3d-nand niet met gestapelde dies. Fabrikanten stapelen al jaren meer dan één die, plakjes silicium dus, op elkaar in een package. Een dergelijke package is de 'chip' die je op het printplaatje gesoldeerd ziet. Bij gestapelde dies worden de afzonderlijke siliciumchips via extreem dunne draadjes buitenlangs met elkaar en de bga-connector onderop verbonden. Er is een tussenvorm waarbij through silicon via's of tsv's gebruikt worden om een deel van de verbindingen te verzorgen. Bij 3d-nand gaan de transistors al in het silicium de hoogte in en bovendien kunnen afzonderlijke dies gestapeld worden binnen een package.

Aansturing

Het is inmiddels wel duidelijk dat een nandchip uitlezen niet zo eenvoudig is en een controller om dat netjes te regelen is dan ook een cruciaal onderdeel. Natuurlijk zitten er op de nandchip zelf ook al diverse onderdelen om een en ander in het gareel te houden. Zo zijn er niet alleen de fgt's, maar ook transistors om source- word- en bit-lines te selecteren. Ook zijn delen gereserveerd voor de opslag van ecc-data en reserve voor als er cellen stukgaan.

De bits zijn georganiseerd in pages, waarbij elke page een klein percentage overcapaciteit heeft, dat voor ecc-data en als reserve dient. Voor de adressering is een deel van het nand als register ingericht en een groep pages is weer samengebracht in een block. Lezen gebeurt op pageniveau, terwijl schrijven op het veel grovere blockniveau gebeurt. De blocks zijn weer in planes samengebracht en een die, of chip, bevat een of meer planes. In een package zijn verschillende dies of chips opeengestapeld en die communiceren weer met de controller.

Het uitlezen en beschrijven van nandflash gebeurt vrij grofkorrelig per page, maar wissen vindt op veel grotere schaal plaats. Om te wissen worden vele pages tegelijk, op blockniveau, gewist. Dat wil je dus zoveel mogelijk beperken, wegens de schade die de hoge benodigde spanningen voor het tunnelen teweegbrengen. Daar komt de controller om de hoek kijken; die moet zo intelligent mogelijk het aantal schrijf- en wisoperaties beperken.

Wanneer je data wil wijzigen, moet dat op pageniveau gebeuren, maar dan zou het hele block waar die page inzit gewist moeten worden en moet de gewijzigde data geschreven worden. Wissen wordt beperkt door data op pageniveau te markeren als oude, of invalid, data. De gewijzigde page wordt naar een lege page gekopieerd en de oude page wordt nog even niet gewist. Zo probeert de controller alle pages die gewijzigd worden in een block eerst naar een lege page te schrijven en pas dan het block te wissen.

Wear levelling en garbage collection

De controller moet ervoor zorgen dat alle blocks ongeveer even vaak gewist worden, een proces dat wear leveling genoemd wordt. Er moeten dus lijsten bijgehouden worden van blocks en hoe vaak ze gewist zijn. Soms betekent dit dat data die weinig verandert actief, zonder dat het echt nodig is, naar een andere page in een ander block verplaatst moet worden.

/i/2001004529.jpeg?f=imagenormal)

Ook oude, invalid pages in een block moeten bijgehouden worden en de controller moet bijhouden welke pages goede en welke invalid data bevatten. Via een proces dat garbage collection genoemd wordt, moeten invalid pages verzameld worden, tot er genoeg in een block bij elkaar zitten om een erase cycle te verantwoorden. Soms houdt dat in dat valide data in een page naar een ander block gekopieerd moet worden. Bovendien is overprovisioning nodig zodat er voldoende lege ruimte is om complete blocks leeg te kunnen maken om ze te kunnen wissen.

/i/2001004531.png?f=imagenormal)

Die twee huishoudelijke taken om het nand te beheren, van data die naar andere blocks wordt verplaatst door het wear-levelling-algoritme en data die door het garbage-collection-algoritme wordt verplaatst, leiden tot extra schrijfacties. Dat proces staat bekend als write amplification, en een goede balans tussen write amplification, wear levelling en garbage collection is cruciaal voor zowel de levensduur als de prestaties van een ssd. Leuk detail: zelfs als je alleen data van een ssd leest, zal de controller schrijfacties moeten verrichten. Een fenomeen dat read disturb genoemd wordt, waarbij het lezen van bits verstoringen in het elektrische veld van naburige bits teweegbrengt, kan na een aantal keer de betrouwbaarheid van de opgeslagen data verminderen. Om die te garanderen moet data na een bepaald aantal keer naar lege pages worden gekopieerd.

Om al die huishoudelijke taken te volbrengen is het niet verwonderlijk dat de controller zo'n grote rol speelt in de prestaties en levensduur van een ssd. Niet alleen de hardware van die controller, zoals het aantal ARM-cores en hun kloksnelheid, en het aantal kanalen, maar ook de firmware is van groot belang. Het zijn immers de block-mapping-, wear-levelling-, en garbage-collectionalgoritmes die de uiteindelijke prestaties dicteren.

Interfaces en formfactors

We hebben gezien hoe nand opgebouwd is, en hoe het wordt aangestuurd op transistor- en controllerniveau. Maar hoe zit het nu met de verschillende formfactors of de producten die je daadwerkelijk in je pc of laptop stopt?

In eerste instantie waren ssd's eigenlijk alleen maar solid-statevarianten van harde schijven, voor zover je pc dat kon zien. De formfactor was daar ook naar; op een enkele 3,5"-variant na waren de meeste ssd's gevat in een 2,5"-behuizing, zoals we die van laptopschijven kennen. En net als een harde schijf werden ze aangesloten op een serial ata-bus, waarbij de vroege ssd's via een sata-300-poort, goed voor snelheden tot 300MB/s, werden aangesloten. In 2009 kwam sata-600, ook bekend als 'sata revisie 3.0', met een bandbreedte van 6Gbit/s beschikbaar en lange tijd was dat de standaardinterface voor ssd's.

Laptops werden echter steeds compacter en vooral platter, waardoor er voor een 9,5mm of zelfs 7mm hoge 2,5"-drive geen ruimte meer was. Fabrikanten weken daarom uit naar een compacter formaat: de msata-interface, of mini-sataconnector. Ssd's werden ontdaan van hun 2,5"-behuizing en kale printplaten werden in de msata-slots gestoken. Die slots leken op een pci-e mini-card-interface, maar dan met sata-interface. Echt succesvol was deze aansluiting niet, deels doordat hetzelfde slot, maar elektrisch anders aangesloten, gebruikt werd voor mininetwerkkaarten.

Laptops werden echter steeds compacter en vooral platter, waardoor er voor een 9,5mm of zelfs 7mm hoge 2,5"-drive geen ruimte meer was. Fabrikanten weken daarom uit naar een compacter formaat: de msata-interface, of mini-sataconnector. Ssd's werden ontdaan van hun 2,5"-behuizing en kale printplaten werden in de msata-slots gestoken. Die slots leken op een pci-e mini-card-interface, maar dan met sata-interface. Echt succesvol was deze aansluiting niet, deels doordat hetzelfde slot, maar elektrisch anders aangesloten, gebruikt werd voor mininetwerkkaarten.

Hoewel msata van een fysieke mini-pci-express-aansluiting gebruikmaakt, biedt de sata-600-interface natuurlijk maar beperkte bandbreedte. En juist dat werd in de laatste jaren steeds meer een bottleneck voor de prestaties van ssd's; bijna alle solid state drives halen wel sequentiële overdrachtssnelheden van zo'n 550MB/s, sneller kan niet. De bandbreedte van een pci-express-interface zou uitkomst bieden. Per pci-e 2.0-lane is er immers 500MB/s aan bandbreedte beschikbaar en voor pci-e 3.0 is dat zelfs bijna het dubbele.

Om van die bandbreedte gebruik te maken werd de m2-standaard ontwikkeld: nog compacter dan msata, maar met een potentiële bandbreedte van zes en een half keer die van sata-interfaces. Er was echter één probleem; controllers konden alleen nog met sata-interfaces overweg, dus kregen we een overgangsperiode waarin m2-ssd's nog steeds via sata werden aangesloten. Dat geeft nogal wat verwarring; je kunt dus een m2-slot op je moederbord hebben en een ssd kopen die er niet op werkt. Verschillen in keying, of uitsparingen in de connector, moeten onderscheid maken tussen een sata- en een pci-e-interface.

Om van die bandbreedte gebruik te maken werd de m2-standaard ontwikkeld: nog compacter dan msata, maar met een potentiële bandbreedte van zes en een half keer die van sata-interfaces. Er was echter één probleem; controllers konden alleen nog met sata-interfaces overweg, dus kregen we een overgangsperiode waarin m2-ssd's nog steeds via sata werden aangesloten. Dat geeft nogal wat verwarring; je kunt dus een m2-slot op je moederbord hebben en een ssd kopen die er niet op werkt. Verschillen in keying, of uitsparingen in de connector, moeten onderscheid maken tussen een sata- en een pci-e-interface.

Er zijn ook adapters verkrijgbaar die een m2-slot geschikt maken voor zogeheten u2-kabels; je kunt dan een 2,5"-ssd via pci-e aansluiten. Daarmee vervangt u2 de sata-express-standaard, die nooit van de grond is gekomen. Een van de beperkingen van die standaard is de bandbreedte; via sata express zijn slechts twee pci-e-lanes beschikbaar, terwijl dat via m2 en u2 vier lanes zijn.

Maar we zijn er nog niet. Alle bovenstaande ssd's moeten natuurlijk niet alleen fysiek aangesloten worden via een sata-, msata- of m2-interface, maar ook nog via een protocol aangestuurd worden. Alle sata- en msata-ssd's werden via het ahci-protocol aangestuurd, net als harde schijven. Ssd's kunnen echter ook efficiënter worden aangestuurd met het nvme-protocol. Dat werd speciaal ontwikkeld voor ssd's en maakt gebruik van hun sterke punten, zoals parallellisme en lage toegangstijden.

Net als bij de overgang van (m)sata naar m2 en pci-express-lanes waren ook de controllers nog niet geschikt voor nvme. Deze non-volatile memory host controller interface specification werkt alleen met ssd's die via pci-express worden aangesloten. In de loop van 2015 zijn de eerste drives voor consumenten met voor nvme geschikte controllers op de markt verschenen en in de komende tijd zullen er meer volgen.

Zo zijn we eigenlijk pas onlangs aangekomen bij een manier om ssd's efficiënt en snel genoeg op onze pc's aan te sluiten om ze optimaal te kunnen benutten. Van ahci over sata, via ahci over pci-express naar nvme over pci-express: een verbetering van minstens tien keer de bandbreedte.

Voorbij 3d-nand en nvme

Als we naar de evolutie van harde schijven kijken, ligt er voor de komende tijd nog een flinke ontwikkeling van ssd's in het verschiet. In de relatief korte tijd dat ssd's voor de gewone consument bereikbaar zijn, hebben we een snelle ontwikkeling gezien, niet alleen wat prestaties betreft, maar vooral wat hun prijs en capaciteit betreft.

Ook de controllers zijn sterk verbeterd. Waar oudere ssd's vooral geplaagd werden door prestatiedegradatie door suboptimale wear levelling en garbage collection, zijn sata-ssd's inmiddels van leeg tot compleet vol even snel. Ook de snelheden van sata-ssd's zijn redelijk gesatureerd; elke ssd die je koopt, loopt tegen de limiet van de sata-600-interface aan. Dat neemt niet weg dat sommige fabrikanten trucs toepassen om de snelheid kortstondig te verbeteren. Sommige sturen het mlc-nand aan als slc-nand en dat is, zoals we gezien hebben, rapper dan mlc-nand. Als die cache vol is, dalen de prestaties echter.

De interface en het protocol om de ssd's aan te sturen zijn beide ook in de loop der tijd verbeterd. We gingen van relatief trage sata-300- en later sata-600-interfaces naar pci-express in de vorm van een volwaardig slot of een kleiner m2-slot. Het protocol bleef lange tijd gelijk aan dat van harde schijven, namelijk ahci, maar daarin is onlangs verandering gekomen met de eerste nvme-drives die via nvmhci worden aangestuurd. Daarmee is de bandbreedte verveelvoudigd en de manier van aansturen geoptimaliseerd voor nand.

/i/2001004565.png?f=imagenormal) In de toekomst zal 3d-nand voor opslag de norm worden. De scaling van 2d-nand heeft met 15nm zo'n beetje de limiet bereikt, terwijl we met 3d-nand zelfs zonder een kleiner procedé steeds verder de hoogte in kunnen om grotere bitdichtheden te realiseren. Tel daar nog enkele stapjes procedéverkleiningen bij en ssd's met capaciteiten van vele terabytes liggen aan de horizon. Niet voor niets zijn ssd's gegroeid van enkele tientallen gigabytes naar 1 of 2 terabyte en fabrikanten hebben al veel grotere ssd's, groter ook dan met harde schijven mogelijk is, aangekondigd.

In de toekomst zal 3d-nand voor opslag de norm worden. De scaling van 2d-nand heeft met 15nm zo'n beetje de limiet bereikt, terwijl we met 3d-nand zelfs zonder een kleiner procedé steeds verder de hoogte in kunnen om grotere bitdichtheden te realiseren. Tel daar nog enkele stapjes procedéverkleiningen bij en ssd's met capaciteiten van vele terabytes liggen aan de horizon. Niet voor niets zijn ssd's gegroeid van enkele tientallen gigabytes naar 1 of 2 terabyte en fabrikanten hebben al veel grotere ssd's, groter ook dan met harde schijven mogelijk is, aangekondigd.

Dat neemt niet weg dat de zoektocht naar het ideale geheugen, dat tegelijk niet-volatiel is, willekeurig te lezen en beschrijven is, weinig energie behoeft en zeer snel is, verdergaat. Welke techniek dat moet worden, phase change-memory, magnetic ram, ferroelectric ram, resistive ram of een andere techniek die in ontwikkeling is: we weten het nog niet. Een kandidaat waarvan nog dit jaar producten moeten verschijnen is Intels 3d XPoint-geheugen, een soort phase-change-geheugen, dat zonder transistors werkt. De techniek moet aanvankelijk als laag tussen ram en ssd gebruikt gaan worden.

/i/2001015091.jpeg?f=imagenormal)

De eerste vorm van ram is waarschijnlijk een crt, of cathode ray tube. Jawel, eenzelfde buis als in twintigste-eeuwse tv's en monitors zat, werd net na de Tweede Wereldoorlog gebruikt als digitale opslag. Deze Williams-Kilburnbuis maakte gebruik van de kortstondige, residuele lading die op de fosforlaag van een crt achterblijft. Die lading werd gemeten met een metalen plaat voor de buis en zo konden bits opgeslagen worden. Echt betrouwbaar werkte dat niet en de techniek was geen lang leven beschoren.

De eerste vorm van ram is waarschijnlijk een crt, of cathode ray tube. Jawel, eenzelfde buis als in twintigste-eeuwse tv's en monitors zat, werd net na de Tweede Wereldoorlog gebruikt als digitale opslag. Deze Williams-Kilburnbuis maakte gebruik van de kortstondige, residuele lading die op de fosforlaag van een crt achterblijft. Die lading werd gemeten met een metalen plaat voor de buis en zo konden bits opgeslagen worden. Echt betrouwbaar werkte dat niet en de techniek was geen lang leven beschoren./i/2001003657.jpeg?f=imagenormal)

Een goedkoper ram is dram; de bits worden opgeslagen in de elektrische lading van een condensator en een enkele transistor doet dienst als schakelaar om de condensator te vullen of leeg te laten lopen. Lading in condensators opslaan heeft als nadeel dat de lading weglekt en dus ververst moet worden. Dit 'dynamische proces' leidt tot de naam dram, of dynamic ram: veel goedkoper om te maken en prima voor werkgeheugen.

Een goedkoper ram is dram; de bits worden opgeslagen in de elektrische lading van een condensator en een enkele transistor doet dienst als schakelaar om de condensator te vullen of leeg te laten lopen. Lading in condensators opslaan heeft als nadeel dat de lading weglekt en dus ververst moet worden. Dit 'dynamische proces' leidt tot de naam dram, of dynamic ram: veel goedkoper om te maken en prima voor werkgeheugen./i/2001003763.png?f=imagenormal) Bij erasable prom, of eprom, werden voor het eerst transistors met een floating gate gebruikt. Die floating gate nam de taak van het metalen contact over en kon dus elektronisch beïnvloed worden. Het legen van de lading in de gate moest met uv-licht gebeuren door een karakteristiek venstertje in de chips en kon alleen voor de hele chip gedaan worden. Met de komst van eeprom kon het wissen met een elektrisch signaal plaatsvinden. Daar was een extra transistor voor nodig, wat het geheugen weer duurder maakte. Het grote voordeel is dat niet de hele chip gewist hoeft te worden, maar slechts een groep bytes.

Bij erasable prom, of eprom, werden voor het eerst transistors met een floating gate gebruikt. Die floating gate nam de taak van het metalen contact over en kon dus elektronisch beïnvloed worden. Het legen van de lading in de gate moest met uv-licht gebeuren door een karakteristiek venstertje in de chips en kon alleen voor de hele chip gedaan worden. Met de komst van eeprom kon het wissen met een elektrisch signaal plaatsvinden. Daar was een extra transistor voor nodig, wat het geheugen weer duurder maakte. Het grote voordeel is dat niet de hele chip gewist hoeft te worden, maar slechts een groep bytes./i/1300351442.jpeg?f=imagenormal) In nandgeheugen ten slotte worden nand-gates gebruikt, maar (opnieuw) Toshiba bedacht een manier om de kosten verder te drukken. Door niet elke geheugencel individueel via een bit- en word-line aan te spreken, maar de word-lines door de verschillende cellen of bits te laten lopen, kon flink op de signaallijnen bespaard worden. De transistors staan dus in serie en per streng wordt een adreslijn gedeeld en hebben de cellen alleen individuele bitlijnen. Nandgeheugen wordt voor ssd's gebruikt en op de volgende pagina's bekijken we hoe nand werkt en welke verschillende typen nand er zijn.

In nandgeheugen ten slotte worden nand-gates gebruikt, maar (opnieuw) Toshiba bedacht een manier om de kosten verder te drukken. Door niet elke geheugencel individueel via een bit- en word-line aan te spreken, maar de word-lines door de verschillende cellen of bits te laten lopen, kon flink op de signaallijnen bespaard worden. De transistors staan dus in serie en per streng wordt een adreslijn gedeeld en hebben de cellen alleen individuele bitlijnen. Nandgeheugen wordt voor ssd's gebruikt en op de volgende pagina's bekijken we hoe nand werkt en welke verschillende typen nand er zijn./i/2001003821.png?f=imagenormal)

/i/2001004439.png?f=imagenormal)

/i/2001004465.png?f=imagenormal)

/i/2001004471.png?f=imagenormal)

/i/2001004495.gif?f=imagenormal)

/i/2001004497.png?f=imagenormal)

/i/2001004507.jpeg?f=imagenormal)

Verwar 3d-nand niet met gestapelde dies. Fabrikanten stapelen al jaren meer dan één die, plakjes silicium dus, op elkaar in een package. Een dergelijke package is de 'chip' die je op het printplaatje gesoldeerd ziet. Bij gestapelde dies worden de afzonderlijke siliciumchips via extreem dunne draadjes buitenlangs met elkaar en de bga-connector onderop verbonden. Er is een tussenvorm waarbij through silicon via's of tsv's gebruikt worden om een deel van de verbindingen te verzorgen. Bij 3d-nand gaan de transistors al in het silicium de hoogte in en bovendien kunnen afzonderlijke dies gestapeld worden binnen een package.

Verwar 3d-nand niet met gestapelde dies. Fabrikanten stapelen al jaren meer dan één die, plakjes silicium dus, op elkaar in een package. Een dergelijke package is de 'chip' die je op het printplaatje gesoldeerd ziet. Bij gestapelde dies worden de afzonderlijke siliciumchips via extreem dunne draadjes buitenlangs met elkaar en de bga-connector onderop verbonden. Er is een tussenvorm waarbij through silicon via's of tsv's gebruikt worden om een deel van de verbindingen te verzorgen. Bij 3d-nand gaan de transistors al in het silicium de hoogte in en bovendien kunnen afzonderlijke dies gestapeld worden binnen een package.

/i/2001004529.jpeg?f=imagenormal)

/i/2001004531.png?f=imagenormal)

Laptops werden echter steeds compacter en vooral platter, waardoor er voor een 9,5mm of zelfs 7mm hoge 2,5"-drive geen ruimte meer was. Fabrikanten weken daarom uit naar een compacter formaat: de msata-interface, of mini-sataconnector. Ssd's werden ontdaan van hun 2,5"-behuizing en kale printplaten werden in de msata-slots gestoken. Die slots leken op een pci-e mini-card-interface, maar dan met sata-interface. Echt succesvol was deze aansluiting niet, deels doordat hetzelfde slot, maar elektrisch anders aangesloten, gebruikt werd voor mininetwerkkaarten.

Laptops werden echter steeds compacter en vooral platter, waardoor er voor een 9,5mm of zelfs 7mm hoge 2,5"-drive geen ruimte meer was. Fabrikanten weken daarom uit naar een compacter formaat: de msata-interface, of mini-sataconnector. Ssd's werden ontdaan van hun 2,5"-behuizing en kale printplaten werden in de msata-slots gestoken. Die slots leken op een pci-e mini-card-interface, maar dan met sata-interface. Echt succesvol was deze aansluiting niet, deels doordat hetzelfde slot, maar elektrisch anders aangesloten, gebruikt werd voor mininetwerkkaarten. Om van die bandbreedte gebruik te maken werd de m2-standaard ontwikkeld: nog compacter dan msata, maar met een potentiële bandbreedte van zes en een half keer die van sata-interfaces. Er was echter één probleem; controllers konden alleen nog met sata-interfaces overweg, dus kregen we een overgangsperiode waarin m2-ssd's nog steeds via sata werden aangesloten. Dat geeft nogal wat verwarring; je kunt dus een m2-slot op je moederbord hebben en een ssd kopen die er niet op werkt. Verschillen in keying, of uitsparingen in de connector, moeten onderscheid maken tussen een sata- en een pci-e-interface.

Om van die bandbreedte gebruik te maken werd de m2-standaard ontwikkeld: nog compacter dan msata, maar met een potentiële bandbreedte van zes en een half keer die van sata-interfaces. Er was echter één probleem; controllers konden alleen nog met sata-interfaces overweg, dus kregen we een overgangsperiode waarin m2-ssd's nog steeds via sata werden aangesloten. Dat geeft nogal wat verwarring; je kunt dus een m2-slot op je moederbord hebben en een ssd kopen die er niet op werkt. Verschillen in keying, of uitsparingen in de connector, moeten onderscheid maken tussen een sata- en een pci-e-interface.

/i/2001004565.png?f=imagenormal)

:strip_icc():strip_exif()/i/2002065593.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2001682215.jpeg?f=fpa_thumb)

:strip_icc():strip_exif()/i/2001559743.jpeg?f=fpa_thumb)

/i/2001190117.png?f=fpa_thumb)

/i/1349425400.png?f=fpa)

:strip_exif()/i/1286274802.jpeg?f=fpa)

/i/1217925693.png?f=fpa)

/i/2000867515.png?f=fpa)