AMD heeft een sse5-instructieset gepubliceerd die vanaf 2009 in de Bulldozer-core te vinden moet zijn. De uitbreidingen moeten voor betere prestaties zorgen en het schrijven van code vereenvoudigen.

Zowel Intel als AMD voorzien hun processors van steeds meer cores, maar het duurt lang voor de softwareindustrie hier optimaal van gebruikmaakt. De verwerking van single-threaded-code kan ondertussen wel een duw in de rug gebruiken, en onder ander sse5 moet hier voor zorgen. Vooral veeleisende applicaties zullen baat hebben bij sse5 en volgens AMD maken de extensies het schrijven van code een stuk makkelijker. De sse-extensies zorgen volgens AMD voor vijf keer zo hoge prestaties bij aes-encryptie en een verbetering van dertig procent bij dct, een wiskundige bewerking die gebruikt wordt bij audio- en videocodecs.

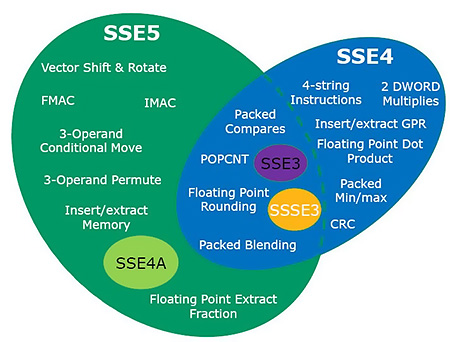

Met de sse5-instructieset gaat AMD de concurrentie aan met Intel die de sse4-instructieset heeft ontworpen. De functionaliteit van sse4 en sse5 overlapt elkaar deels, maar verschillende instructies die wel aanwezig zijn in sse4 zijn niet aanwezig in sse5, en omgekeerd. Verwacht wordt dat Intel niet voor sse5 zal kiezen.

Een van de verbeteringen die AMD noemt in de specificaties van zijn 'AMD64 Technology 128-Bit SSE5 Instruction Set', is de ondersteuning voor 3- en 4-operand-instructies. Hiermee kan een programmeur een extra register benaderen waarmee de bewerking op twee andere registers kan worden beïnvloed. Zonder deze functionaliteit zouden hiervoor meerdere operaties nodig zijn. Dankzij deze uitbreiding komt de sse5-instructieset op bijna gelijke voet te staan met de AltiVec-instructieset die deze functionaliteit al langer biedt. Verschil is wel dat bij sse5 één van de inputregisters gebruikt moet worden om het resultaat op te slaan terwijl AltiVec hier een apart register voor biedt. In totaal biedt sse5 ruim honderd nieuwe instructies waarmee bewerkingen op vectoren versneld kunnen worden.

/i/1241443636.png?f=fpa)

:strip_exif()/i/1187160107.jpg?f=fpa)

:strip_exif()/i/1153907652.jpg?f=fpa)

:strip_exif()/i/1181810633.jpg?f=fpa)

/i/1185456771.png?f=fpa)

:strip_exif()/i/1170598652.jpg?f=fpa)