Op Memforum.org is een presentatie van Intel verschenen over een nieuwe geheugenarchitectuur, ontworpen in samenwerking met de JEDEC, te weten FB-DIMM. Deze architectuur is ontworpen om in de toekomst gebruikt te worden in servers om grotere geheugencapaciteiten en hogere snelheden mogelijk te maken. Het grote verschil tussen het huidige geheugen en de FB-DIMM's is de aansturing van de modules. Er wordt gebruik gemaakt van een point-to-point verbinding tussen de geheugenmodules in plaats van een gedeelde bus, wat een aantal voordelen heeft.

Bij een gedeelde geheugenbus zorgt elke aansluiting voor een geheugenmodule op een signaallijn voor storing. Hierdoor is het aantal modules dat aangesloten kan worden op één geheugencontroller beperkt. Hierbij komt dat bij hogere kloksnelheden het aantal modules dat zonder problemen aangesloten kan worden naar beneden zakt waardoor de huidige architectuur steeds lastiger wordt in serveromgevingen waar men vaak vele gigabytes aan geheugen wilt hebben.

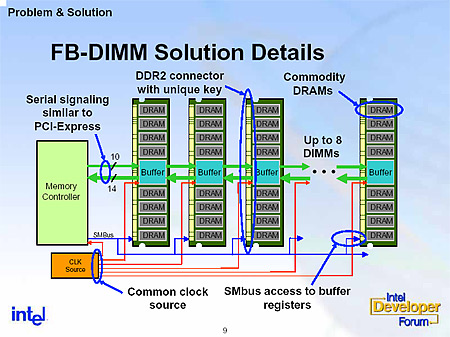

Bij FB-DIMM's zit een point-to-point verbinding tussen de modules waardoor maximaal acht modules aangesloten kunnen worden op één controller. Daarnaast zijn hier een stuk minder signaallijnen nodig wat het ontwerp van moederborden veréénvoudigt. Zo zou een systeem met 48 FB-DIMM's minder signaallijnen nodig hebben dan een DDR2-geheugencontroller met slechts 4 DIMM's. Hierdoor wordt het logischerwijs een stuk gemakkelijker om een server uit te rusten met een flinke hoeveelheid geheugen.

Wat betreft de prestaties zou het geheugen volgens de slides van Intel ook goed mee kunnen komen. Bij lage datarates heeft normaal DDR2-geheugen een lagere latency, maar zodra de datarate omhoog gaat worden de rollen omgedraaid. Daarnaast kan het FB-DIMM geheugen gemakkelijker hogere datarates halen. In de slides wordt bijvoorbeeld een DDR2-configuratie met 8GB geheugen vergeleken met een FB-DIMM configuratie met dezelfde capaciteit. Hierbij scoort het DDR2-geheugen circa 6,5GB/sec terwijl het FB-geheugen een score van 8,2GB/sec neerzet.

Niet alleen moet de nieuwe geheugenarchitectuur sneller zijn en hogere capaciteiten bieden, het moet ook betrouwbaarder zijn. De doelstelling van Intel is om slechts éénmaal per honderd jaar een ongedetecteerde error te laten plaatsvinden. Om dit te verwezenlijken is er onder andere CRC-beveiliging aanwezig op commando's en data en zijn andere nieuwe RAS-features aanwezig.