Onderzoekers van MIT en Analog Devices hebben een 16bit-processor gemaakt met 14.000 zogenoemde carbon nanotube field-effect transistors. Het gaat om de grootste chip op basis van koolstofnanobuisjes tot nu toe.

De onderzoekers hebben de chip de naam RV16XNano gegeven en opgebouwd op basis van de opensource-RISC-V-architectuur. Hoewel het om een, naar huidige maatstaven, vrij basale processor gaat, is deze in staat een set van instructies accuraat uit te voeren. Zo lukte het de onderzoekers om met een programma het bericht 'Hello, World! I am RV16XNano, made from CNTs' te genereren.

Volgens het MIT bouwt het wetenschapsteam voort op onderzoek dat zes jaar geleden resulteerde in een 1bit-chip met 178 carbon nanotube field-effect transistors, of cnfets. In de periode nadien zijn er flinke vorderingen gemaakt op het gebied van het terugdringen van onder andere materiaal- en fabricagedefecten.

Metallische vervuiling maakt dat een klein deel van de koolstofnanobuisjes het correct laten schakelen van de transistors vertraagt of stopt. Metallische cnt's zijn altijd geleidend en het draait om het krijgen van halfgeleiders. Voor een werkende chip van enige omvang en complexiteit, moet de puurheid van de gebruikte koolstofnanobuisjes op 99,999999 procent liggen.

Dankzij een set technieken die de onderzoekers Dream hebben gedoopt, kunnen ze functionele chips maken, ook als de puurheid op 99,99 procent ligt. Dream staat voor designing resiliency against metallic cnt's. De basis van de methode ligt bij het simuleren van verschillende gatecombinaties om te achterhalen welke robuust zijn en welke, door defecten, niet. Bij het ontwerpen van de chip gebruikten ze vervolgens een programma dat automatisch alleen de robuuste combinaties inzet.

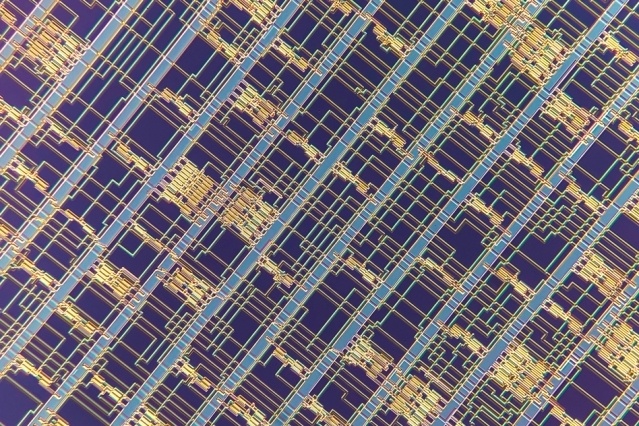

Daarnaast hebben de onderzoekers het fabricageprocedé verbeterd. Voor het maken van cnfets worden koolstofnanobuisjes in een oplossing aangebracht op een wafer met daarop de transistorarchitectuur. Om samenklonteren van buisjes te voorkomen, is de wafer behandeld met een middel dat de hechting bevordert en ook brengen de onderzoekers een specifieke polymeercoating aan waarna de wafer ondergedompeld wordt in een oplossing. Deze laatste stap maakt dat de polymeer, en daarmee de klonteringen van buisjes, weggespoeld wordt. De onderzoekers noemen deze stap Rinse, removal of incubated nanotubes through selective exfoliation.

Ten slotte wisten ze gecontroleerd eigenschappen van transistors te bepalen die maken dat het om n- of p-type transistors gaat. Dat was een van de uitdagingen bij transistors op basis van koolstofnanobuisjes. De onderzoekers slaagden erin door onder andere titanium of platina aan te brengen. De techniek noemen ze Mixed, wat staat voor metal interface engineering crossed with electrostatic doping.

De minuscule buisjes van koolstof in een hexagonaal raster van kippengaas zijn licht, sterk en in theorie goedkoop te produceren, en hebben goede geleidende eigenschappen. Ze worden daarom al jaren gezien als potentiële opvolger van silicium als materiaal voor chips, die er sneller mee zouden kunnen worden bij lagere warmteproductie. Onderzoekers liepen tegen tal van obstakels aan bij het daadwerkelijk produceren van chips, maar volgens de onderzoekers van het MIT is het nu niet meer de vraag of, maar wanneer chips op basis van koolstofnanobuisjes verschijnen. Max M. Shulaker van het onderzoeksteam denkt zelfs dat dit binnen vijf jaar het geval kan zijn, onder andere doordat ze dezelfde fabricagetechnieken gebruiken als de huidige chipindustrie.

De onderzoekers publiceren hun werk in het wetenschappelijke tijdschrift Nature onder de titel Modern microprocessor built from complementary carbon nanotube transistors.

:strip_exif()/i/2003038918.jpeg?f=imagemedium)

:strip_exif()/i/2003038920.jpeg?f=imagemedium)

/i/2003162792.png?f=fpa)

/i/1233067786.png?f=fpa)

:strip_exif()/i/1286274802.jpeg?f=fpa)