De halfgeleiderdivisie van de Japanse elektronicafabrikant heeft een techniek ontwikkeld om transistors van nanodraden te bouwen die 16nm groot zijn. De techniek zou problemen met lekstromen moeten reduceren.

Een van de grootste problemen met het verkleinen van transistors is de lekstroom; naarmate de onderdelen, en vooral de gates, kleiner worden, is er minder diëlektrisch materiaal om als elektrische isolator te fungeren. Het gevolg daarvan is dat de transistors lekstromen ondervinden, wat de verdere verkleining van de transistors bemoeilijkt. Diverse manieren om lekstromen het hoofd te bieden zijn al ontwikkeld, waaronder het gebruik van high-k-diëlektrums, strained silicium en het gebruik van extra lagen om de gate te isoleren.

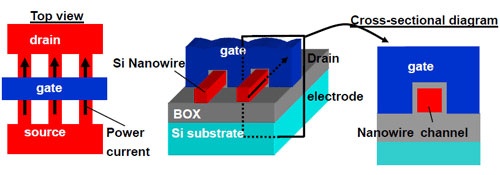

Toshiba heeft een transistor ontwikkeld op basis van nanodraden die lekstromen moeten voorkomen. De silicium nanodraden dienen als channel tussen de source en de drain in de transistors, waarbij de gate om de channels heen wordt gewikkeld. De zijwanden van de gate werden van 30 naar 10nm gereduceerd, wat een toename van de stroom in de aan-toestand van 40 procent mogelijk maakt. Ook een verandering in de kristallijne structuur van het silicium in de nanodraad-channel draagt bij aan een prestatieverbetering van 25 procent. De transistors halen zo een aan-stroom van 1mA/µm, volgens Toshiba een record voor nanodraad-transistors. De lekstroom bedraagt daarbij 100nA/µm.

Toshiba zal de techniek donderdag tijdens een vlsi-symposium demonstreren. Het bedrijf denkt dat het zijn transistors op relatief korte termijn geschikt kan maken voor praktische toepassingen op 16nm-nodes.

/i/1302857598.png?f=fpa)

:strip_exif()/i/1203362676.gif?f=fpa)

/i/1282050173.png?f=fpa)

/i/1203534091.png?f=fpa)

/i/1260965273.png?f=fpa)

/i/1250157415.png?f=fpa)

/i/1242207182.png?f=fpa)

:strip_exif()/i/1045165316.gif?f=fpa)

:strip_exif()/i/1168970761.gif?f=fpa)