Zowel ARM als Toshiba presenteerden tijdens een symposium hun plannen om chips zuiniger te maken: ARM zegt de energieconsumptie van zijn processors met de helft te kunnen reduceren en Toshiba werkt aan zuiniger geheugenchips.

De vorderingen op het gebied van energiebeheer werden door beide bedrijven gepresenteerd tijdens de International Solid State Circuits Conference. Volgens onderzoekers van ARM Holding is het mogelijk om processors met de ARM-architectuur tot vijftig procent zuiniger te maken, uitgaande van chips die volgens een 65nm-procedé worden geproduceerd. De techniek die de bezuinigingen mogelijk moet maken, werd door de onderzoekers Razor gedoopt, en grijpt aan op verschillende niveaus van het chipontwerp.

Razor omvat een combinatie van verschillende technieken. Het behelst onder meer de toepassing van detectieschakelingen voor het opsporen van timingfouten en methodes voor foutcorrectie. Onder de Razor-vlag valt ook een techniek om de processorspanning precies op de gebruikte klokfrequentie af te stemmen. De techniek werd getest op ARM-processors die op de bestaande manier werden ontworpen en door de Taiwanese fabrikant United Microelectronics werden geproduceerd. De 65nm-chips met Razor zouden bij een klokfrequentie van 1GHz 52 procent minder energie verstoken dan chips zonder Razor-techniek.

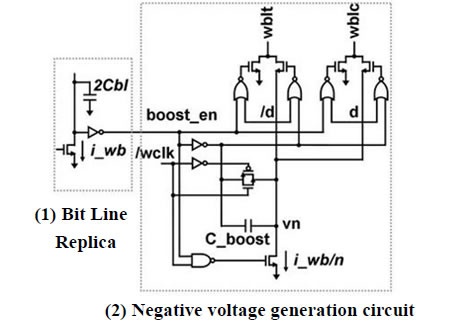

Ook Toshiba presenteerde zijn vorderingen op het gebied van energiebesparing. De techniek van de Japanse hardwarefabrikant zou een lagere werkspanning van sram zonder een toename van het aantal fouten mogelijk maken. Statisch geheugen zou op 0,7V kunnen functioneren; dat zou moeten leiden tot een lager energieverbruik van digitale apparatuur.

Ook respectievelijk NTT en Intel presenteerden hun vindingen om hardware zuiniger te maken. Eerstgenoemde zag kans een op 90nm gebakken dualcore cmos-netwerkprocessor te ontwikkelen die slechts 24mW verstookt. Gigant Intel verbeterde de datadoorvoer van een op 1,3GHz werkende 45nm-chip met 12 tot 23 procent.

/i/1203534091.png?f=fpa)

:strip_exif()/i/1046975813.jpg?f=fpa)

/i/1230888156.png?f=fpa)

/i/1248857907.png?f=fpa)

/i/1263550627.png?f=fpa)

/i/1263379166.png?f=fpa)

/i/1249049772.png?f=fpa)

/i/1245053638.png?f=fpa)

/i/1237280952.png?f=fpa)

/i/1246288357.png?f=fpa)