Onderzoekers denken Moore's Law voor transistors nog wat verder te kunnen rekken door terug te grijpen op vacuümtechniek. De eerste transistors met een vacuümkanaal zijn al geproduceerd en zouden onder meer voor communicatie ingezet kunnen worden.

Het nieuwe type transistor werd door medewerkers van het Ames-onderzoekscentrum, onderdeel van NASA, ontwikkeld. De vacuümkanaal-transistors zouden in communicatie-apparatuur ingezet kunnen worden: hun ontwerp maakt zeer hoge snelheden mogelijk die met traditionele silicium mosfets niet haalbaar zijn. Het eerste prototype van de onderzoekers haalde een schakelsnelheid van 460GHz, waarmee de transistors in de terahertz-band voor zenders en ontvangers gebruikt zouden kunnen worden.

Zover is het echter nog niet: het prototype werkt nog met een spanning van 10V, wat te hoog is voor gebruik met normale transistors. Door het ontwerp aan te passen, zouden de 'vacuümtransistors' echter met vergelijkbare spanningen als normale transistors kunnen werken en samen op chips ondergebracht kunnen worden. De productie van de vacuümtransistors is daarvoor al geschikt: standaardproductietechnieken die in de halfgeleiderindustrie worden ingezet, zijn ook geschikt voor de productie van de vacuümtransistors.

De transistors werken op een deels vergelijkbare manier als de vacuümbuizen. de voorlopers van moderne transistors: ze hebben echter niet de nadelen van die buizen. Zo hoeven ze niet op te warmen omdat er geen warme kathode nodig is. Bovendien hoeft in het kanaal helemaal geen vacuüm te heersen: over de kleine afstanden is zo'n vacuüm helemaal niet nodig maar kan helium gebruikt worden. De onderzoekers maken de afstand tussen anode en kathode zo kort, dat de kans op botsingen tussen elektronen en gasmoleculen laag is. Bovendien hebben de elektronen met de gebruikte spanningen te weinig energie om heliummoleculen aan te slaan. De ionen die daarbij gevormd zouden worden, zouden de kathode kunnen beschadigen.

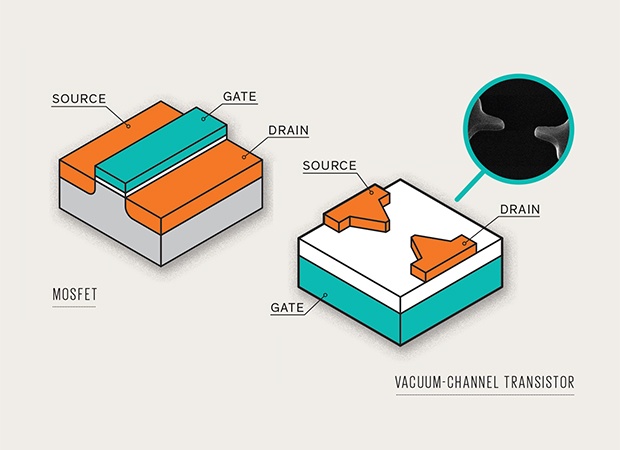

De vacuümtransistors werken grotendeels als gewone mosfet, met een gate-elektrode die de stroom tussen de kathode en anode, ofwel de source en drain, regelt. De source- en drain-elektrodes zijn scherpe elektrodes, waartussen elektronen kunnen oversteken. Daarbij ondervinden ze geen hinder van botsingen, zoals in een halfgeleidermateriaal in traditionele transistors. De onderzoekers gaan zich nu richten op het ontwerp van circuits met een groot aantal van deze vacuümtransistors, waarbij waarschijnlijk mems-technieken gebruikt moeten worden om de juiste heliumatmosfeer te waarborgen.

/i/2000588502.png?f=fpa)

/i/1353410017.png?f=fpa)

/i/1233067786.png?f=fpa)

/i/1252054477.png?f=fpa)