Toshiba heeft de ontwikkeling aangekondigd van een soc met 64 cores voor embedded toepassingen. De 40nm-chip is opgebouwd uit twee clusters van 32 cores en heeft dedicated hardware voor beeldverwerking aan boord.

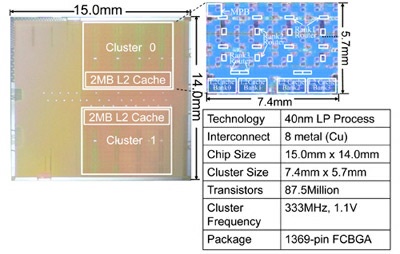

De nieuwe Toshiba-soc wordt geproduceerd op een 40nm-lp-procedé met acht koperlagen voor de interconnect. De chip heeft een oppervlakte van in totaal 210mm², terwijl de twee 32core-clusters elk 42mm² daarvan innemen. De kloksnelheid van de clusters is vastgesteld op 333MHz, waarmee in totaal 1,5Tops berekend kunnen worden. Dit is veertien keer zo veel als de octocore-soc die Toshiba voor het eerst op de ISSCC 2008-beurs aankondigde. Die chip maakte gebruik van een 65nm-procedé.

Behalve door gebruik van een kleiner procedé heeft Toshiba het energieverbruik van de 64core-soc nog op andere manieren laag gehouden. Zo kunnen ongebruikte delen van de chip gedeactiveerd worden en maakt Toshiba gebruik van zijn eigen, energiezuinige data-mapping flip-flop circuit. Ook is de chip voorzien van hardware om het afspelen van videocontent te versnellen. Het decoderen van een h264-1080/30p-filmpje zou daardoor slechts een vermogen van 500mW opslurpen. Voor de communicatie tussen de cores wordt gebruikgemaakt van network on a chip-technologie.

Toshiba wil de nieuwe 'many-core'-soc inzetten voor onder meer de automobielindustrie, maar ook voor consumentenproducten. Hiervoor heeft Toshiba speciale hardware voor beeldherkenning geïntegreerd op de chip. Tevens kan de chip 4k2k-videocontent met een framerate van 15fps verwerken met een verbruik van minder dan 800mW. Toshiba geeft meer details over de chip op de '2012 IEEE Symposia on VLSI Technology and Circuits', die van 12 tot en met 14 juni plaatsvond in Honolulu.

:strip_icc():strip_exif()/i/1355987138.jpeg?f=fpa_thumb)

/i/1347385226.png?f=fpa)

/i/1309767168.png?f=fpa)

/i/1236852193.png?f=fpa)

/i/1317197896.png?f=fpa)

:strip_exif()/i/1296474747.gif?f=fpa)

/i/1299143559.png?f=fpa)

/i/1203534091.png?f=fpa)