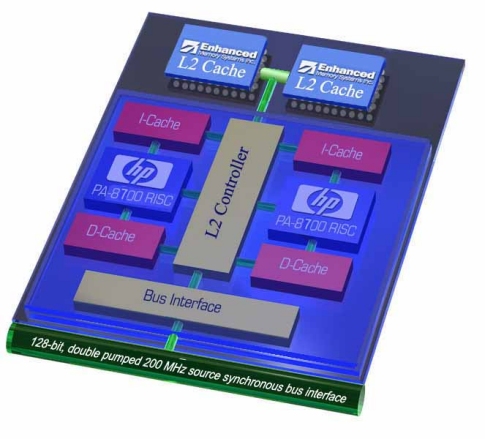

Hoewel HP samen met Intel de architectuur en instructieset voor de Itanium lijn heeft ontwikkeld en op lange termijn haar eigen serie processors wil stilzetten hebben de mensen van de ontwerpafdeling niet uit hun neus zitten eten. Op het microprocessor forum werden details van de PA-8800 RISC vrijgegeven. Deze high-end serverchip bevat 330 miljoen transistors, verdeeld over twee 1GHz PA-8700 cores, totaal 3MB L1 cache en een duizelingwekkende 32MB L2 cache. Het artikel gaat vooral in op de manier waarop de ontwerpers erin zijn geslaagd om zo'n groot L2 cache, dat ook nog eens gedeeld moet worden, te implementeren. Omdat 32MB puur SRAM 1,8 miljard transistors en dus enorme kosten zou betekenen, is het door de technici verdeeld over vier aparte 600MHz chips van een speciaal type "1 Transistor SRAM", die samen een 128 bit bus moeten vullen. Geschatte minimale SpecInt/SpecFP2000 scores zijn 900/1000. Het single-chip SMP systeem heeft een 6,4GB/s verbinding met de buitenwereld, die 100% compatible is met de bus van de Itanium:

With the new PA-8800 RISC processor, HP is going a different route, that is, instead of using physically separate processors, the new concept involves placing two entire PA-8700 CPU cores in the same package. There is a certain sacrifice in terms of flexibility with such a concept since a single CPU cannot be purchased, on the other hand, since nobody uses a single CPU in a dual system anyway, it is actually a smart move that further solves a variety of problems, particularly since it enables the use of a shared L2 cache with high bandwidth access to the cache by both cores, which eliminates the bottleneck of the system / memory bus for access of valid data.

|

Bedankt voor de tip burne.