Uitzicht op het IDF (geel verlicht) vanaf de hotelkamer op de 29e verdieping

Maandag: internationale persdag

15:30 PST: De eerste dag van het IDF was gereserveerd voor internationale pers en omvatte verschillende presentaties. Om duidelijke redenen wordt het echt belangrijke nieuws bewaard tot iedereen er bij is, maar toch was er gelegenheid om met een aantal interessante mensen te praten. De dag werd geopend door Justin Rattner, de CTO van Intel. Hij hield een verhaal over de 'many core'-strategie, en bevestigde nogmaals Intels visie van 'minstens tientallen, misschien wel honderden' cores per processor in de toekomst. Het plakken van meerdere cores op één chip is op zich niet moeilijk, maar de omliggende uitdagingen zoals onderlinge communicatie, bandbreedte, zuinigheid en niet te vergeten de software zijn dat wel.

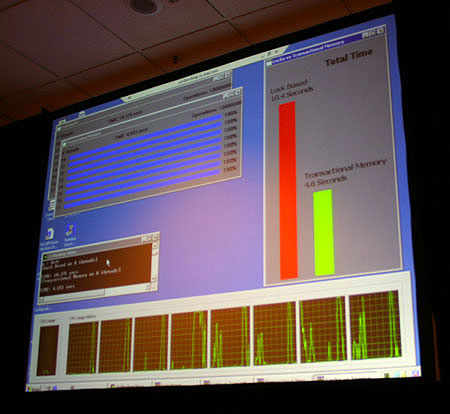

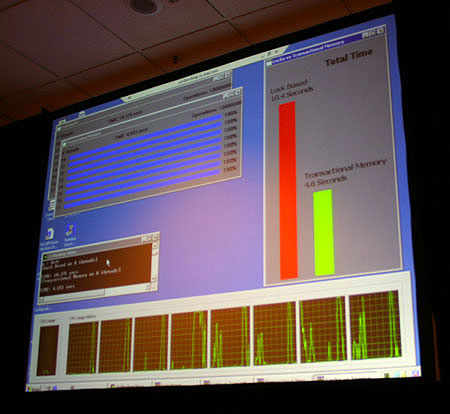

Een van de dingen waar aan gewerkt wordt is Transactional Memory, een concept dat is geleend van databases. Het doel van deze techniek is om software die meerdere threads in hetzelfde geheugen laat werken sneller te maken, door zogenaamde locks te vervangen. Een lock is op dit moment nodig om te garanderen dat er geen datacorruptie ontstaat tijdens het wijzigen van gedeelde gegevens. Stel bijvoorbeeld dat een bank twee betalingen verwerkt vanaf dezelfde rekening, dan moeten beide bedragen van het saldo worden afgetrokken. Als dat echter parallel gebeurt dan lezen beide threads eerst het oude saldo in, en schrijven ze even later een nieuw saldo terug. Als de threads echter niet van elkaar afweten zal effectief maar één bedrag van de rekening zijn afgehaald, en wel degene die toevallig het laatste werd verwerkt. Met een lock kan dit soort problemen voorkomen worden: het blokkeert de executie van andere threads om te garanderen dat de thread die de lock aanvraagt de enige is die op dat moment met de gegevens rommelt.

Het probleem van locks is dat het slecht is voor de prestaties: het blokkeren van threads maakt immers korte metten met het hele idee van parallelle berekeningen. Ook kan het tot vervelende bugs leiden: als twee threads op elkaar staan te wachten is er sprake van een 'deadlock', die niet oplosbaar is. Transactional Memory lost dit op door bij te houden welke variabelen door welke threads in gebruik zijn, en conflicten automatisch op te lossen. Het is dus niet meer nodig om standaard alle andere threads stil te leggen; dat zal alleen nog maar gebeuren als het echt nodig blijkt, en dan nog zonder dat de programmeur zich er druk om hoeft te maken. Met een puur softwarematige implementatie van dit systeem in Java werd een prestatiewinst van ongeveer zestig procent getoond bij het gebruik van acht threads. Een hardwarematig versnelde uitvoering van Transactional Memory zou volgens de simulaties van het bedrijf zelfs drie tot vier keer sneller kunnen zijn dan locken - op een server met zestien processors.

Een andere aankondiging die werd gedaan was die van een nieuw algoritme om CRC-checks mee uit te voeren. Dit is voornamelijk interessant voor servers die grote ladingen (enkelen tot tientallen gigabits) netwerkverkeer te verwerken krijgen. Het berekenen van checksums om te controleren of de ontvangen data tijdens het verzenden niet corrupt is, is een essentieel onderdeel van het afhandelen van netwerkverkeer - maar ook iets wat bij hoge snelheid veel processorkracht eet. Onderzoekers van Intel hebben zich over dit probleem gebogen en een veel efficiëntere implementatie van de CRC-checksum bedacht dan tot nu toe is gebruikt. Het zogenaamde 'Slice by Eight' (SB8) algoritme heeft slechts 2,2 kloktikken per ontvangen byte nodig, terwijl de huidige implementaties ongeveer 7 cycles per byte nodig hebben. Volgens de presentator lijkt het nieuwe idee erg voordehandliggend als je het eenmaal ziet, maar was het daarvoor 'utterly uninventable'. Intel maakt een implementatie van het algoritme open source beschikbaar via SourceForge, en heeft het ook aan Microsoft gedoneerd.

Na de presentaties was het tijd voor een lunch, waar aan iedere tafel iemand van Intel zat om over een bepaalde techniek te praten. Aan onze tafel was dat Simon Ellis, die werkt aan de UDI-standaard. Hij beschrijft de Universal Display Interface als HDMI voor de pc. De twee standaarden moeten elkaar aanvullen en in de loop der jaren steeds dichter naar elkaar toe groeien. Verschillen tussen de technieken zijn dat UDI géén geluid meeneemt, kleiner stekkers gebruikt en vooral goedkoper te implementeren is. In tegenstelling tot bij DVI kent UDI geen maximale resolutie of refresh rate. Hoeveel pixels er per seconde verstuurd kunnen worden is direct afhankelijk van de beschikbare bandbreedte, en die kan van apparaat tot apparaat (en per kabel) verschillen. De standaarduitvoering voor consumenten zal op 2 of 3 gigabit werken, maar een professionele versie van 5 tot 8 gigabit is ook al in aantocht. Versie 1.0 van de specificatie wordt in het tweede kwartaal van het jaar verwacht.

UDI (links) en HDMI (rechts)

Na de lunch worden we uitgenodigd om deel te nemen aan een test van 'Seamless access'. In ruil voor een visitekaartje krijgen we een week toegang tot drie of vier draadloze netwerken tussen het hotel en het IDF. De 'Seamless access' moet ervoor zorgen dat onze notebooks automatisch tussen de verschillende accesspoint en providers wisselen tijdens de tocht. Handig als je tijdens de vijf minuten durende wandeling je e-mail wil checken  . Tijdens de volgende presentatie zit ik samen met een Belg, twee andere Nederlanders en Zweed aan een tafel, en allemaal proberen we onze nieuwe 'Seamless access' aan de praat te krijgen, maar zonder veel succes. Na een uur lukt het iemand om in te loggen, maar de rest had het al opgegeven.

. Tijdens de volgende presentatie zit ik samen met een Belg, twee andere Nederlanders en Zweed aan een tafel, en allemaal proberen we onze nieuwe 'Seamless access' aan de praat te krijgen, maar zonder veel succes. Na een uur lukt het iemand om in te loggen, maar de rest had het al opgegeven.

Volgende punt op de agenda was de CMOS radio, oftewel een radiozender geïntegreerd in een normale processor. Het voordeel van het inbouwen boven een aparte chip is niet alleen dat het goedkoper en zuiniger wordt, maar ook dat er meerdere standaarden ondersteund kunnen worden. De eerste chip met radio werd al langere tijd geleden getoond, maar enkele weken terug heeft men de eerste chip met MIMO (meerdere antennes) gedemonstreerd. Met het standaard 90nm-procédé werd een 108 megabit WiFi-chip gebakken. Er werden nog een hoop andere dingen besproken, maar vanwege tijdgebrek zullen die nu even niet besproken worden.

Maandag: mobility showcase

17:50 PST: Na de technische sessies werden we door Intel vervoerd naar het penthouse van het Fairmont hotel. De enorme suite is onder andere bekend vanwege een scene uit de film 'The Rock' die er is opgenomen, en er hebben bekende figuren zoals president Kennedy, Arnold Schwarzenegger en Charles en Dianna overnacht. Nu had het de twijfelachtige eer om het decor te vormen voor tweehonderds nerds die zich aan laptops stonden te vergapen.

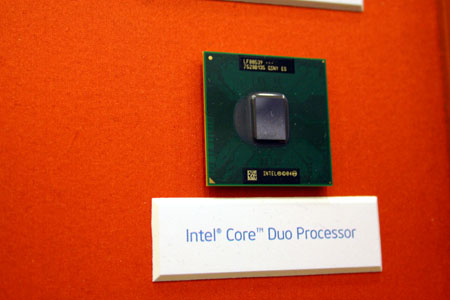

Doel van Intel was om te laten zien welk Centrino Duo-notebooks er allemaal waren en welke applicaties er allemaal gebruik kunnen maken van dualcore. Er waren ook mensen van Skype aanwezig, maar geen van hen had antwoorden op vragen over de 'exclusieve' feature voor Intel-processors, die pas geleden is gekraakt om ook op AMD te werken.

Maandag: AMD

23:30 PST: Na de mobility showcase was het haasten om de vorige twee pagina's van het weblog online te krijgen, aangezien er direct erna een afspraak was gemaakt met AMD. Het grootste nieuws dat ze daar te melden hadden was de introductie van de 2,6GHz dualcore Opteron x85. Er was tevens een 'demonstratie' van een dual Socket F-server, maar dat was iets dat we maar op hun woord moesten geloven: er was zowel aan de hardware als aan de software die er op draaide niets te zien waaruit bleek dat het om iets nieuws ging. Niet dat we AMD niet geloven, maar iets meer dan een dicht chassis was toch wel leuk geweest.

Een van de dingen die AMD tegelijk met de introductie van DDR2 gaat doen is ervoor zorgen dat het geheugen betrouwbaarder wordt. ECC-foutcorrectie is al sinds het begin aanwezig in de Opteron, maar de nieuwe core houdt precies bij hoeveel fouten iedere DIMM maakt, en als dat er te veel worden zal hij de overtreder uitschakelen. Eventueel kan er op dat moment zelfs een reservereepje worden ingeschakeld om de gemiste capaciteit op te vangen. Over de prestaties van de nieuwe DDR2-Opteron (codenaam: Santa Rosa) wilde het bedrijf geen concrete uitspraken doen. Sowieso is het afhankelijk van het soort applicatie, maar over het algemeen werd wel gezegd om niets heel spectaculairs te verwachten.

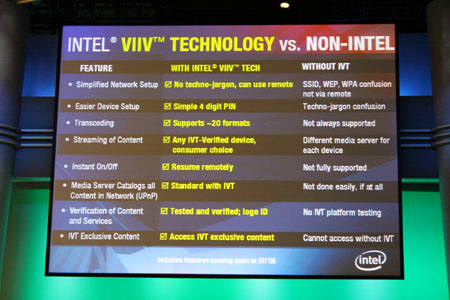

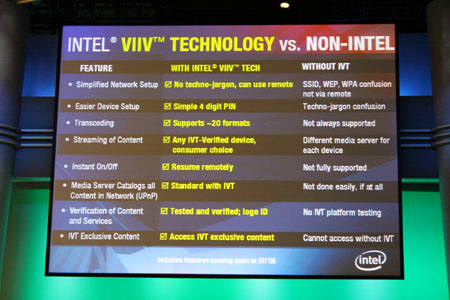

Een andere demonstratie was die van een AMD Live, de bijna schaamteloze kopie van Intels Viiv. Een pc met Live-sticker moet aan de volgende eisen voldoen: dualcore AMD-processor op Socket AM2, 1GB of meer geheugen, Windows MCE, DirectX 9-videokaart, SATA-schijf en dvd-brander. Als de processor een high-end FX-model is moeten er bovendien een tweede videokaart en harde schijf aanwezig zijn in de machine. Draadloos toetsenbord/muis en tv-tuner zijn optioneel. Verder was de dualcore Turion 64 X2 aanwezig, maar nog steeds niet in de vorm van echte notebooks. Twee referentiemodellen met chipsets van respectievelijk ATi en nVidia waren echter wel te bewonderen. De nVidia-plank (groen) was voorzien van SLI, en als we een sticker die op de rode plank zat mogen geloven draaide de Turion op 1,8GHz.

Dinsdag: keynote Justin Rattner

7:00 PST: Vandaag zullen alle keynotes zo ongeveer achter elkaar worden gegeven. Dit in tegenstelling tot de twee vorige jaren, toen de presentaties nog over de verschillende dagen werden verspreid. Het wordt dus een erg lange zit, waarvan op deze pagina een 'live' verslag zal worden bijgehouden (in ieder geval zolang de accu van de notebook het uithoudt en het draadloze internet niet overbelast raakt door iedereen die hetzelfde probeert te doen  ). Voordeel is wel dat de rest van dagen volledig beschikbaar is voor technische sessies en het beursgedeelte.

). Voordeel is wel dat de rest van dagen volledig beschikbaar is voor technische sessies en het beursgedeelte.

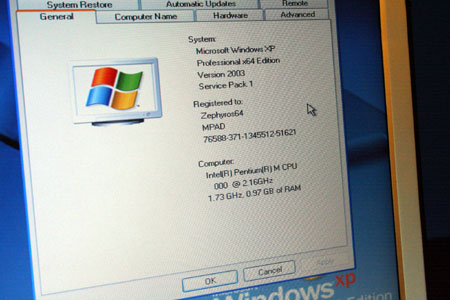

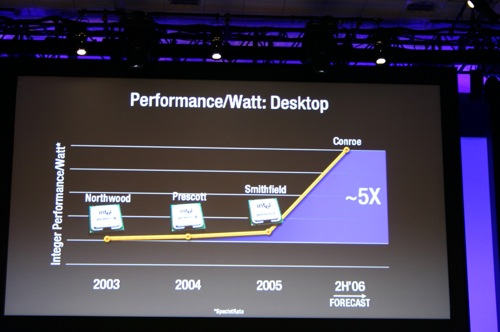

9:00 PST: De keynote van Justin Rattner begint met toe te geven dat Intel last heeft gehad van stevige concurrentie, maar benadrukt dat de negatieve trend qua stroomverbruik al is doorbroken met de Pentium M-architectuur, en de nieuwe 'Core Microarchitecture' (ja, dat is de officiele naam voor de NGMA) moet dat verder gaan verbeteren. De nieuwe core wordt gekenmerkt door vijf belangrijke kenmerken: Wide Dynamic Execution, Advanced Digital Media Boost, Intelligent Power Capability, Advanced Smart Cache en Smart Memory Access. De chip kan tot drie 128 bit SSE-instructies in één cycle uitvoeren. Dat levert de volgende verbeteringen op ten opzichte van de bestaande processors (gemeten met SPECintRate).

| | Relatief aan | Prestaties | Stroomgebruik |

|---|

| Merom | Core Duo T2600 | +20% | Gelijk |

| Conroe | Pentium D 950 | +40% | -40% |

| Woodcrest | Paxville 2,8GHz | +80% | -35% |

Met de nieuwe architectuur is de processor niet langer de grootste bron van stroomverbruik, maar moet vooral de rest van het platform aangepakt worden. Er werd een scherm gedemonstreerd dat niet om de zoveel milliseconden door het OS ververst hoeft te worden, waardoor het verbruik van een ultra-portable systeem van 6,5 naar 3 watt daalt. Vervolgens werd getoond dat zelfs het hele moederbord tijdelijk uitgeschakeld kan worden om het verbruik terug te brengen naar 1 watt.

Dinsdag: keynote Pat Gelsinger

Vervolgens is Pat Gelsinger aan de beurt, die Woodcrest, Conroe en Merom laat zien. Het volgende punt op de agenda is een 'modeshow' van Pentium M-blades en -servers. Ook is er een storageplatform te zien dat tot 2TB aan opslag in RAID5 biedt, aangestuurd door een Xscale-processor.

De volgende aankondiging is die van Intel Virtualization Technology for Directed I/O (VTD), de volgende generatie van virtualisatie. Net als AMD gaat Intel dus niet alleen de processor zelf, maar ook de randapparaten virtueel beschikbaar maken. De directeur van VMware komt dan het podium op om persoonlijk haar steun voor de techniek aan te kondigen. Dit jaar zullen alle producten van VMware de eerste generatie van VT ondersteunen, en gedurende 2007 zal de tweede generatie (VTD) daaraan toegevoegd worden.

Het volgende punt op de agenda is een nieuw wereldrecord TPC-C voor 4-way systemen, dat is gezet door IBM met dualcore Xeon MP 7000-processors gebaseerd op de Paxville-core. De Xeon MP is de enige processor die niet op korte termijn over zal stappen op de nieuwe Core-architectuur, en er zijn dit jaar dus niet zulke grote verbeteringen te verwachten. Wel zal de Xeon MP overstappen naar 65nm-productie en 16MB L3-cache krijgen.

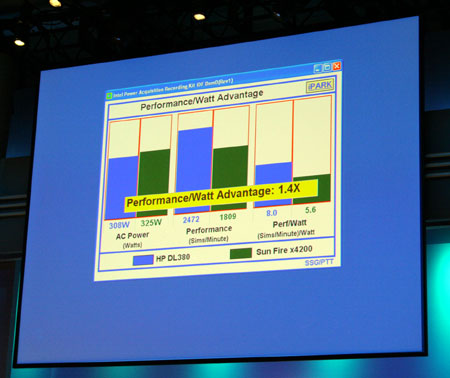

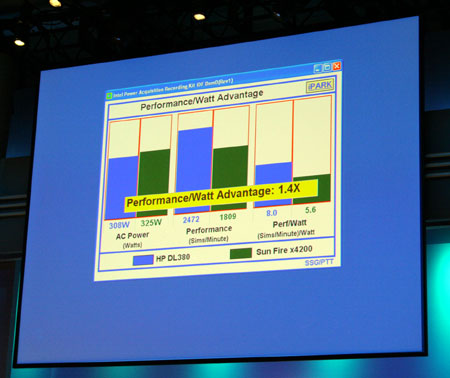

De volgende gast is HP, dat het nieuwe Xeon DP-platform (Bensley) toont, met een dubbele 3GHz Woodcrest aan boord. Deze wordt ter plekke getest tegen een server van Sun met Opteron 280-processors (2,4GHz). Uit de benchmarks moet het publiek concluderen dat de nieuwe Intel-server 1,4 keer betere prestaties per watt biedt. Vervolgens worden drie ogenschijnlijk identieke Dell-servers getoond die wel gebruikmaken van hetzelfde platform, maar toch onder de kap verschillende processors hebben: de eerste was voorzien van Dempsey, de volgende van Woodcrest, en de laatste had de quadcore Clovertown-chips aan boord. Dit is om aan te tonen dat de verschillende generatie processors makkelijk uitgewisseld kunnen worden.

Daarna wordt een chip getoond die het verwerken van XML sneller kan maken. Deze feature zal in de toekomst in alle serverplatforms worden opgenomen.

De volgende bezoeker is Microsoft, dat een demonstratie van Excel 12 en Vista geeft op een Conroe-systeem. Ook wordt de toepassing van AMT (Active Management Technology) getoond in de vorm van de volgende generatie SMS server. Een systeem waarvan de harde schijf gecrashed is wordt via het netwerk gerepareerd door in het BIOS een andere bootschijf te kiezen. Microsoft en Intel gaan samenwerken om van Ws-Management een standaard te maken voor dit soort beheer op afstand. Verder wordt aangekondigd dat toekomstige OSsen van Microsoft ingebouwde ondersteuning gaan bieden voor VT en VTD.

Beveiligingsfeatures zijn het volgende punt op de agenda: de specificatie van LaGrande Technology wordt officieel aangekondigd, en het wordt bekend dat de volgende generatie van AMT een techniek krijgt om uitbraken van virussen te herkennen en tegen te houden. Op het einde wordt bekendgemaakt dat de presentatie op de quadcore 65nm desktopchip Kentsfield heeft gedraaid.

Dinsdag: random impressies

12:05 PST: Even van de lunch gebruikmaken om wat impressies van IDF te posten.

Ontbijt in de perskamer

Vroem

Merom notebook

Oh sorry, mocht ik er niet aankomen? :+

Woodcrest servers

De tweede verdieping van het Moscone Center

Dinsdag: keynote Don MacDonald

16:00 PST: Don MacDonald praatte vooral over Viiv, en demonstreerde naast de voordelen van het bestaande platform ook een paar dingen die toekomstige generaties beter moeten maken. Een van de dingen was een nieuwe manier om apparaten aan het netwerk toe te voegen met behulp van near-field communicatie, die alleen over een afstand van enkele centimeters werkt. Na het detecteren van een nieuwe pda via WiFi was het voldoende om het apparaat even langs het Viiv-systeem heen te zwaaien om alle (beveiligings)instellingen over te nemen. Binnen enkele seconden was de pda opgenomen in het Viiv-netwerk.

Ook wilde hij een demonstratie geven van een Viiv-systeem dat volledig via stemherkenning bediend kon worden. Bij de vierde of vijfde poging van een steeds zenuwachtiger wordende MacDonald herkende het apparaat inderdaad de opdracht om 'Family Guy' op te zoeken in de gids, maar het apparaat moet wellicht dus nog wel iets beter uitgewerkt worden voor het op de markt gebracht wordt  .

.

Een andere leuke feature was een filmposter met geïntegreerde near-field communicatie. Door een pda er bij in de buurt te houden werd een link en trailer doorgestuurd, en terug thuis op het Viiv-netwerk kan de trailer niet alleen op een grote televisie getoond worden, maar in de toekomst mogelijk ook de volledige film aangeschaft worden.

Tot slot werd er een demonstratie gegeven van een Conroe op onbekende snelheid tegenover een Pentium Extreme Edition 3,46GHz in Call of Duty 2, waarbij het huidige topmodel 90 fps haalde en de nieuwe processor 111 fps. Beide systemen waren overigens voorzien van quad SLI. Volgens Intel zou de score van de Conroe overigens nog verder geoptimaliseerd kunnen worden.

Dinsdag: keynote Sean Malony

14:00 PST: Sean Maloney begon zijn mobility keynote met een verhaal over het internet, waarbij steeds meer informatie beschikbaar is en ook steeds meer toegespitst wordt op de gebruiker. Een van de beperkingen die het bedrijf daarbij ziet is dat internet niet 'mobiel' genoeg is - althans niet voor multimediatoepassingen. Dat zou langs drie paden langzaam moeten veranderen: handhelds, notebooks en draadloze communicatietechnieken. Onder de handhelds worden mobiele telefoons en pda's verstaan. De volgende generatie van Xscale-processors draait op ruim 1GHz en heeft extra stroombesparende en prestatieverbeterende features aan boord die specifiek op multimedia zijn gericht. Naast de pda en telefoon zou er dit kwartaal ook nog een nieuw mobiel apparaat moeten verschijnen, de ultra-mobile pc. Volgens de geruchten werkt onder andere Microsoft aan zo'n apparaat, maar daarover werd niets gezegd op IDF.

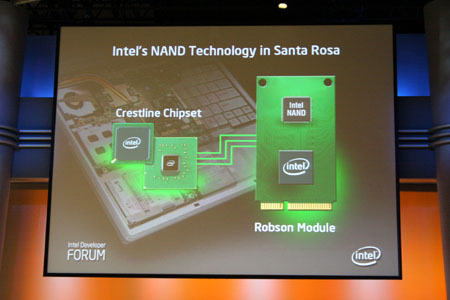

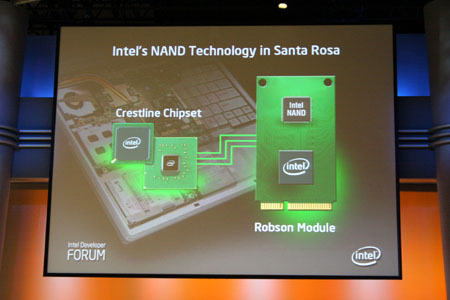

Voor laptops is er natuurlijk de eerder besproken Merom. In de tweede helft van dit jaar zal deze in het huidige Centrino Duo-platform geprikt kunnen worden, maar in de eerste helft van 2007 zal het nieuwe Santa Rosa-platform verschijnen, met onder andere een nieuwe GPU, AMT, 802.11n WiFi en Robson-technologie. Dat laatste is een techniek die NAND-flashchips gebruikt om notebooks sneller te maken. Er werd een directe vergelijking vertoond waarbij een notebook met Robson twee keer zo snel opstartte als die zonder. Ook het opstarten van een hele serie applicaties achter elkaar gebeurde op de machine met Robson veel sneller: hij had er maar 3 in plaats van de 15 seconden van de 'oude' machine voor nodig. Ondertussen werd er - waarschijnlijk omdat de harde schijf minder nodig is - ook nog gemiddeld 0,8 watt bespaard, wat voor een notebook toch verschil kan maken in het aantal minuten dat de accu gebruikt kan worden.

De laatste manier om het internet mobieler te maken is door nieuwe communicatietechniek, zoals 802.11n en WiMax. Er werd een demonstratie gegeven van een live HD-stream die via een 108 megabit draadloos netwerk werd verstuurd. Interessanter was de demonstratie van WiMax, in de vorm van een scooter die een 2 megabit verbinding met internet had. Vanaf de scooter kon live audio en video verstuurd worden, maar ook Google Earth bekeken worden om te helpen bij het vinden van de weg. Intel kondigde de eerste chip aan die WiFi en WiMax combineert in één radio, en zei dat de eerste eindproducten in de tweede helft van dit jaar beschikbaar zullen komen. Het bedrijf vertrouwt er bovendien op dat er een internationale standaard zal komen om de 2,3 - 2,5GHz band vrij te geven voor WiMax, en verwacht dat WiFi en WiMax over twee tot drie jaar zullen samensmelten tot één.

Dinsdag: vraag het aan Intel

17:00 PST: Het volgende punt op het programma was een interview met Dr. Raj Yavatkar, directeur van Intels System Technology Lab. Een van zijn belangrijkste taken van dit moment is om manieren te onderzoeken om het stroomverbruik van alles wat niet de processor zelf is terug te brengen. Hij werkt bijvoorbeeld aan technieken om het stroomverbruik van FB-DIMM terug te brengen door individuele DRAM-chips uit te schakelen als ze niet gebruikt worden. De heetste delen van de gebufferde geheugenrepen (de bufferchips zelf) moeten nog wel aan blijven staan, maar het gemiddelde verbruik van FB-DIMM zou toch mee kunnen vallen. De afweging is echter wel tussen prestaties en zuinigheid: door gegevens over verschillende banken te verdelen kunnen de prestaties verbeterd worden, omdat er dan van meer lokaties tegelijk gelezen kan worden. Het nadeel ervan is wel dat er daarom ook weer minder chips uitgeschakeld kunnen worden, waardoor het stroomverbruik omhoog gaat.

Een ander interessant onderwerp was een scherm dat zijn eigen beeld ververst, zodat de videokaart tijdelijk uitgeschakeld kan worden zolang er niets verandert aan het weergegeven beeld. Huidige notebooks (en desktops overigens ook) verversen het beeld minstens zestig keer per seconde, of er nou iets veranderd is of niet. De techniek werkt door de framebuffer in het scherm zelf te integreren. Het is nog niet mogelijk om slechts een deel van het scherm te updaten, maar dat is wel iets waar naar gekeken wordt voor toekomstige generaties.

Een ander punt waar Yavatkar persoonlijk erg enthousiast over is, zijn efficiëntere voedingen. Volgens zijn onderzoek gaat maar liefst de helft van al het vermogen dat computers nodig hebben al verloren voor het aankomt bij de componenten die het nodig hebben. Dit komt door voedingen en voltage-conversies die niet efficiënt zijn, en beide punten zullen in de toekomst worden aangepakt. De meeste voedingen zijn op dit moment geoptimaliseerd om zo efficiënt mogelijk te zijn bij hun piekvermogen. Onder hun piekvermogen zijn ze echter veel minder goed, terwijl dat eigenlijk helemaal niet nodig is. Het Systems Technology Lab heeft een voeding ontworpen die ook onder zijn maximale vermogen efficiënt blijft, en probeert ervoor te zorgen dat dat ontwerp vaker gebruikt zal worden. Om minder voltage-conversies te doen is het handig als zoveel mogelijk onderdelen van een systeem dezelfde spanning gebruiken. De FB-DIMM-standaard maakt al gebruik van dezelfde spanning als PCI Express, en het wordt verwacht dat ook CSI (Intels toekomstige 'HyperTransport-achtige' platform) dezelfde soort signalen zal gebruiken, hoewel hij daar geen officiële uitspraken over wilde doen. Uiteindelijk moet de efficiëntie van stopcontact tot componenten verbeteren van 50% tot 85%.

18:15 PST: Tijdens Intels multicore panel vroegen we Intel over de betrouwbaarheid van hun toekomstige processors. Met honderden miljoenen tot binnenkort al miljarden transistors in iedere chip wordt het steeds moeilijker om deze helemaal correct te produceren. Tevens zijn de steeds kleinere transistors gevoeliger voor straling, die bitjes kan laten omvallen. De hoge heren van verschillende afdelingen bij Intel bevestigden dat het probleem bestaat. Nu al zijn er technieken als ECC en paritybits die gebruikt worden om fouten in de processors op te vangen en/of te corrigeren. Het gaat dan meestal om bitjes die omvallen in caches. Het punt waarop het risico op rekenfouten groter wordt is nog enkele generaties verwijderd, maar het bedrijf is wel al serieus bezig om onderzoek te doen naar manieren om fouten te herkennen. Dit kan onder andere door berekeningen een tweede keer uit te voeren om te controleren of ze wel goed waren. Dit kan door een andere thread of andere core gedaan worden, maar het nadeel blijft dat er prestaties verloren gaan. Het doorlopende doel is om met technieken te blijven komen die de betrouwbaarheid op zijn minst in stand houden (en waar mogelijk ook verbeteren), maar geen negatieve invloed op de prestaties hebben.

Dinsdag: Technology Showcase

22:30 PST: Een paar foto's van de technology showcase.

Draadloos USB

Waterkoeler van Intel

Microsoft was groots aanwezig met Vista

GDDR4-chip

DDR3-module

FB-DIMM

Notebookconcept voor slachtoffers van de economy class

Toet toet toeter op m'n WiMax scooter

Server met veel harde schijven

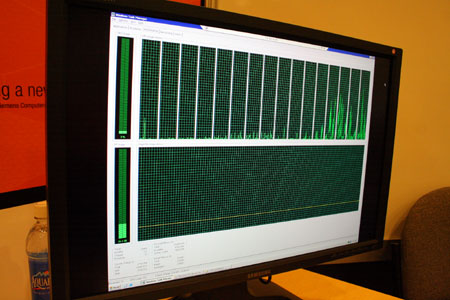

Taskmanager op een 16-way Itanium

Optische SATA-drives, straks noodzakelijk als Intel PATA niet meer ondersteunt.

Deze gadget tovert iedere videokaart om in een triple head. Kost 300 dollar.

Woensdag: I/OAT benchmarks

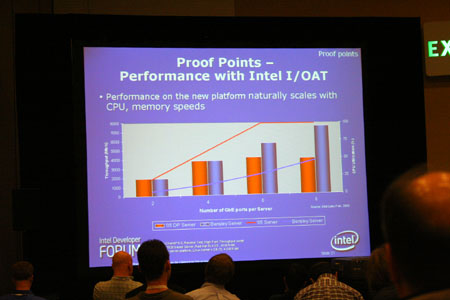

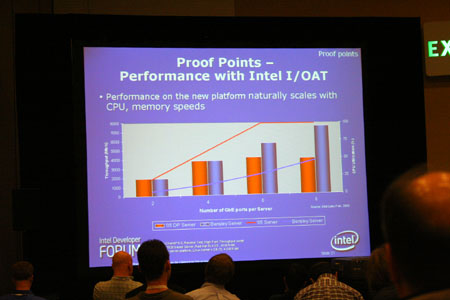

Tijdens een presentatie over I/OAT - Intel I/O Acceleration Technology - werd uitgelegd hoe het systeem werkt. Het probleem dat de techniek op moet lossen is de processorbelasting die wordt veroorzaakt door snelle TCP/IP-verbindingen. Het is een combinatie van technieken in de netwerkkaart, de chipset en het operating systeem ondersteund moeten worden. Het doel is om het aantal keren dat de processor in zijn normale taken onderbroken wordt te minimaliseren.

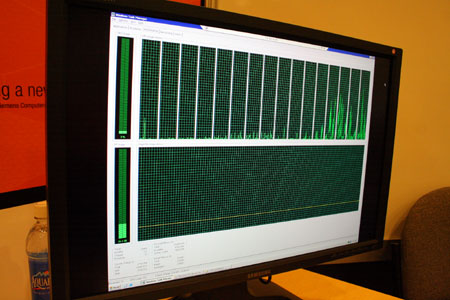

Er werden benchmarks getoond van twee servers met meerdere gigabit ethernetcontrollers. Een server zonder I/OAT kon 2Gbit/s aan dataverkeer afhandelen met een belasting van om en nabij de veertig procent. Met 4Gbit/s verkeer zat het ruim boven de 50%, en een volledige 6Gbit/s verkeer afhandelen was niet eens meer mogelijk, omdat de processor het simpelweg niet aankon. Met I/OAT ingeschakeld zag het plaatje er veel beter uit: 2Gbit/s verkeer had nog minder dan 10% van de processor nodig en bij 8Gbit/s werd pas een belasting van 50% bereikt.

Woensdag: Intels 'spionage' blootgelegd

12:00 PST: Collega Robbin Ooievaar deed gisteren een interessante ontdekking aan de pas die iedere IDF-ganger nodig heeft om toegang te krijgen tot de beurs. Aan de achterkant zit een sticker met een zilveren patroon geplakt, met in het midden een kruisje waar een klein bobbeltje onder was te voelen. Toen viel er ineens een kwartje over de vreemde constructie bij alle deuren die toegang geven tot de sessies. Intel heeft ons onaangekondigd voorzien van RFID-chips. Blijkbaar willen ze van iedereen op het IDF bijhouden waar en wanneer ze naar binnen gaan. Wat ze met die gegevens gaan doen is ons niet bekend. Hoogstwaarschijnlijk gaat het om onschuldige algemene statistieken over de populariteit van de sessies, maar het zou net zo makkelijk zijn om op deze manier iemands persoonlijke gangen na te gaan. Dat hier helemaal niets over is gezegd is ergens toch wel vreemd dus.

Niet dat we er verder een probleem van willen maken, maar het is toch een 'interessant' voorbeeld van hoe het mogelijk is om iemand onopgemerkt een stukje privacy af te nemen. In eerdere jaren werden soortgelijke statistieken verzameld door streepjescodes op de pas te scannen, maar het is vrijwel onmogelijk om dat te doen zonder dat degene die gescanned wordt het merkt. RFID-chips daarentegen zijn zo klein dat ze vrijwel overal in verstopt kunnen worden, en de ontvangers kunnen met een beetje creativiteit ook wel uit het zicht worden opgesteld. Zo is het helemaal niet meer duidelijk waar en wanneer je gevolgd wordt.

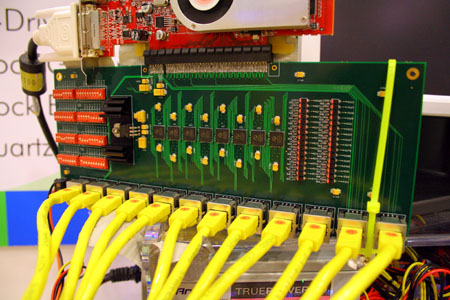

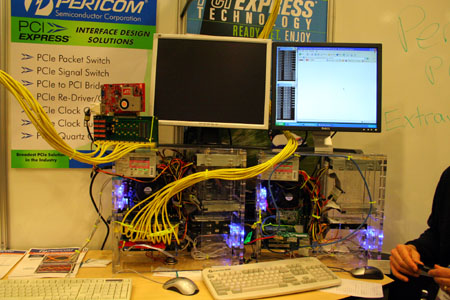

Woensdag: PCI Express via ethernet

Woensdag: de Core-architectuur ontrafeld

Intel heeft vandaag tijdens een speciale dubbele sessie uitgebreide technische details laten zien van de nieuwe Core architectuur. Het bedrijf zegt niet bang te zijn om zulke specifieke details aan (onder andere) de concurrentie te laten zien, omdat het volgens hen minstens 1,5 tot 2 jaar zal duren voor alle features nagemaakt kunnen worden. De nieuwe features van de Core-architectuur zijn door Intel grofweg verdeeld in vijf categorieën:

Wide Dynamic Execution

Wide Dynamic Execution

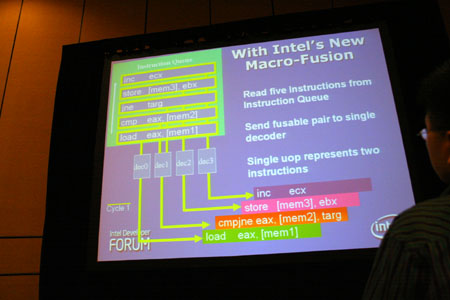

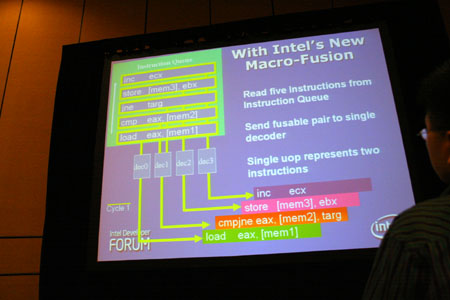

De nieuwe core kan om te beginnen vier in plaats van drie instructies per kloktik decoderen, uitvoeren en verwerken. Omdat het erg moeilijk is om binnen een programma instructies te vinden die onafhankelijk van elkaar uitgevoerd kunnen worden (zonder de werking van de software te veranderen) heeft de Core-core grotere buffers aan boord, zodat er een grotere ruimte is om in te zoeken. De scheduler kan 32 opdrachten tegelijk vasthouden om uit te kiezen. Verder is de branch predection verbeterd en doen de processors aan 'fusion' van instructies op het niveau van micro- en macro-ops. Dat wil zeggen dat iedere keer dat hardware herkent dat er twee instructies vlak achter elkaar staan die eigenlijk net zo goed in één klap uitgevoerd kunnen worden, hij dit ook zal doen. Op deze manier kan het aantal operaties dat wordt uitgevoerd met 10% worden teruggebracht.

Intelligent Power Capability

Intelligent Power Capability

Om de core zuiniger te maken kan zo ongeveer ieder onderdeel in- en uitgeschakeld worden. Er zijn tientallen verschillende gebieden die allemaal alleen maar actief zijn op de momenten dat ze ook daadwerkelijk nodig zijn. Sommige delen (cache, bussen, buffers) kunnen zelfs deels worden uitgeschakeld. Normaalgesproken brengt het uitschakelen van onderdelen een vervelend nadeel met zich mee, namelijk dat het tijd kost om het weer in te schakelen als het nodig is. Hierdoor gaat de reactietijd omhoog en daar kunnen de prestaties dus onder lijden. Intel heeft echter een slim systeem bedacht dat precies voorspelt wanneer het nodig is om een bepaald deel van de chip te activeren. Omdat de pipeline 14 stappen lang is en aan het begin bekend wordt wat een instructie gaat doen, kan er voor gezorgd worden dat de nodige onderdelen een aantal tikken later (als de instructie op het punt staat om uitgevoerd te worden) gereed zijn.

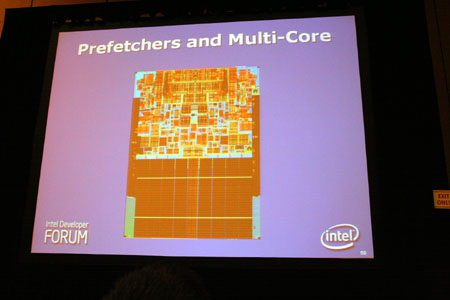

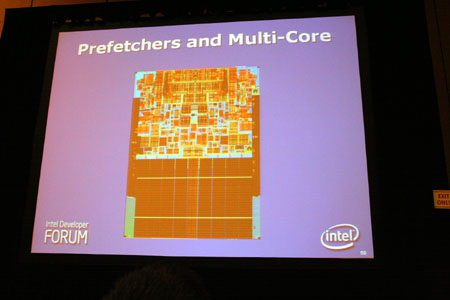

Naast Memory Disambiguation vallen ook betere prefetchers onder dit kopje. Er zijn per L1-cache twee prefetchers aanwezig die ervoor zorgen dat de juiste gegevens uit het L2-cache klaarstaan op het moment dat de instructie uitgevoerd wordt. In het L2-cache zijn nog eens twee prefetchers die ervoor zorgen dat de gegevens uit het systeemgeheugen alvast in het L2-cache komen. Dit alles moet voor een lagere gemiddelde latency zorgen, en dat zonder een geïntegreerde geheugencontroller. Meerdere prefetchers worden overigens gebruikt omdat er meerdere soorten patronen te herkennen zijn. De prefetchers zijn zo intelligent dat ze zelf kunnen beoordelen hoe effectief ze zijn.

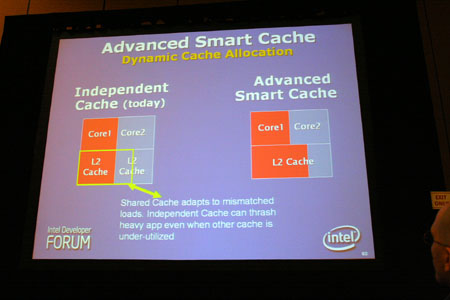

Advanced Smart Cache

Advanced Smart Cache

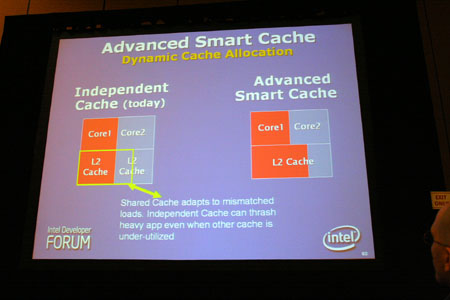

De Core-processors zullen tot 4MB gedeeld L2-cache bieden. Niet alleen kunnen ze op die manier van elkaars gegevens profiteren, maar ook een hoop FSB-bandbreedte besparen. De communicatie tussen de cores onderling loopt namelijk via het cache. Het cache heeft ook een hogere bandbreedte gekregen, en net als bij de huidige Centrino Duo kan de capaciteit per core dynamisch ingesteld worden.

Smart Memory Access

Smart Memory Access

Dit is een van de meeste innovatieve nieuwe features die in de Core-architectuur te vinden is: Memory Disambiguation. Om de correcte uitvoer van een programma te garanderen moeten alle instructies in de juiste volgorde uitgevoerd worden. Er zijn al vele jaren technieken om binnen de processor OOO (out-of-order) te werken, maar het probleem was nog steeds dat alle invoer en uitvoer sequentieel moest gebeuren. Het is immers op zijn zachts gezegd onwenselijk dat de processor al data uit het geheugen gaat lezen terwijl de programmeur er eerst nog een wijziging op uit wilde voeren.

In de praktijk is het bij lange na niet nodig om álle lees- en schrijfacties in de exacte volgorde van het programma uit te voeren, maar de huidige processors kunnen gewoon niet weten wanneer het een probleem vormt, en kunnen dus simpelweg niet het risico nemen om de volgorde van het programma te negeren. Smart Memory Access in de Core zorgt er echter voor dat de hardware deze conflicten wel kan herkennen, zodat het in veel gevallen niet meer nodig is om te wachten met het lezen van data tot alle voorgaande schrijfacties zijn verwerkt. Het gaat daarbij overigens wel om een (conservatieve) voorspelling. Als de Disambiguator de fout in gaat moeten alle instructie na die fout opnieuw worden uitgevoerd, net als bij een fout in de Branch Predictor. De Disambiguator is echter slim genoeg om zelf te weten wanneer hij te veel fouten maakt, en zal zichzelf uitschakelen als dat het geval is.

Advanced Digital Media Boost

Advanced Digital Media Boost

De nieuwe core kan iedere cycle een 128-bit SSE-instructie uitvoeren, terwijl de huidige Intel-chips dat maar één keer per twee cycles kunnen doen. De chip kan maximaal vijf instructies per cycle uitvoeren, waarvan drie SSE. Er zijn acht nieuwe instructies toegevoegd in SSE4 die specifieke multimedia-applicaties zouden kunnen helpen.

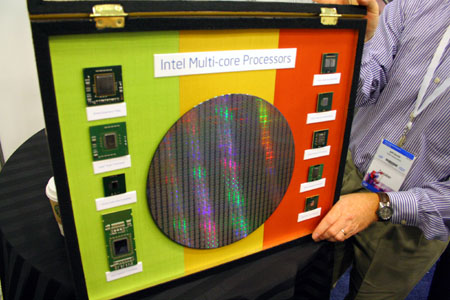

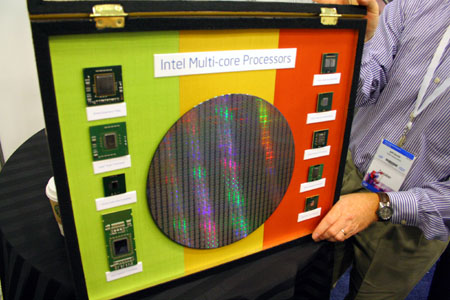

Donderdag: multicore fotofeest

9:45 PST: Plaatjes van verschillende multicorechips.

Conroe 2,66GHz vs. Athlon 64 X2 2,8GHz

Verzameling multicores

65nm Xeon MP Tulsa met 16MB L3

65nm Xeon DP Woodcrest met 8MB L2?

65nm Xeon LV Sossaman met 2MB L2

90nm Itanium 2 Montecito met 24MB L3

65nm Core Duo Yonah met 2MB L2

Intel 90nm Pentium D Smithfield met 2MB L2

Intel 65nm Pentium D Presler met 4MB L2

65nm Core Quatro? Kentsfield met 8MB L2?

Dit jaar is Tweakers.net voor de derde keer uitgenodigd om aanwezig te zijn bij Intels Developer Forum, een internationaal evenement dat niet alleen draait om nieuwe producten, maar ook om het leggen van contacten en het overbrengen van een visie voor de toekomst. Het interessante aan IDF ten opzichte van veel andere evenementen is dat het niet alleen maar draait om marketing- en verkooppraat: het is daarnaast ook echt een bijeenkomst van technische mensen, zowel van Intel zelf als van andere bedrijven. Als er een nieuwe technologie wordt aangekondigd is er bijvoorbeeld vrijwel zeker ook de gelegenheid om vragen te stellen aan de personen die het hebben ontwikkeld of ermee aan het werk zijn. Een typische dag op IDF bestaat niet uit het rondslenteren langs allerlei kraampjes in een enorme hal, maar uit het volgen van presentaties of sessies over onderwerpen die echt enorm uiteenlopen, zowel qua inhoud als qua technisch niveau.

Dit jaar is Tweakers.net voor de derde keer uitgenodigd om aanwezig te zijn bij Intels Developer Forum, een internationaal evenement dat niet alleen draait om nieuwe producten, maar ook om het leggen van contacten en het overbrengen van een visie voor de toekomst. Het interessante aan IDF ten opzichte van veel andere evenementen is dat het niet alleen maar draait om marketing- en verkooppraat: het is daarnaast ook echt een bijeenkomst van technische mensen, zowel van Intel zelf als van andere bedrijven. Als er een nieuwe technologie wordt aangekondigd is er bijvoorbeeld vrijwel zeker ook de gelegenheid om vragen te stellen aan de personen die het hebben ontwikkeld of ermee aan het werk zijn. Een typische dag op IDF bestaat niet uit het rondslenteren langs allerlei kraampjes in een enorme hal, maar uit het volgen van presentaties of sessies over onderwerpen die echt enorm uiteenlopen, zowel qua inhoud als qua technisch niveau.

![]() . Niet lang na aankomst in de zaal begon een enthousiaste jongeman het publiek wat uit te leggen over zijn werk bij Intel. Al op de derde slide van de presentatie ging het echter over naar hele enge dingen: het leek er op dat de beste man een nieuw elektrisch circuit had bedacht waarmee een notebook kan wisselen tussen netstroom en stroom van een of meer accu's. Dat soort dingen bestaan natuurlijk allang, maar die van hem was beter. Of zoiets. Pas op dat moment begon het op te vallen dat er verdacht weinig rode pasjes (pers) aanwezig waren. Een Chinees uitziende man met perspas zat wel driftig te hameren op zijn onbegrijpelijke toetsenbord, maar dat lijkt een soort hobby te zijn voor de Aziaten. Naast hem zat iemand met een pas van AMD, die ook niet erg onder de indruk leek te zijn. Enigszins beschaamd werd de zoektocht naar interessant nieuws weer hervat.

. Niet lang na aankomst in de zaal begon een enthousiaste jongeman het publiek wat uit te leggen over zijn werk bij Intel. Al op de derde slide van de presentatie ging het echter over naar hele enge dingen: het leek er op dat de beste man een nieuw elektrisch circuit had bedacht waarmee een notebook kan wisselen tussen netstroom en stroom van een of meer accu's. Dat soort dingen bestaan natuurlijk allang, maar die van hem was beter. Of zoiets. Pas op dat moment begon het op te vallen dat er verdacht weinig rode pasjes (pers) aanwezig waren. Een Chinees uitziende man met perspas zat wel driftig te hameren op zijn onbegrijpelijke toetsenbord, maar dat lijkt een soort hobby te zijn voor de Aziaten. Naast hem zat iemand met een pas van AMD, die ook niet erg onder de indruk leek te zijn. Enigszins beschaamd werd de zoektocht naar interessant nieuws weer hervat.![]() .

.

/i/1242207182.png?f=fpa)