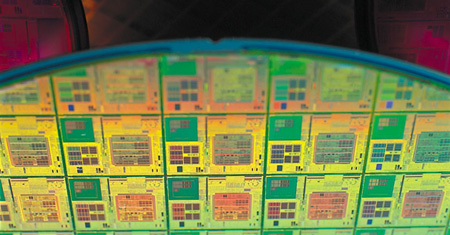

Reuters meldde dat chipdesign-software ontwikkelaar Simplex en elektronicagigant Toshiba bekend hebben gemaakt een nieuwe manier te hebben ontwikkeld voor de wijze waarop transistors in microchips met elkaar kunnen worden verbonden. Deze techniek zou de performance van een chip met 10% kunnen vergroten, het opgenomen vermogen reduceren met 20% en de yields verhogen met 30%. De productiekosten zouden daardoor omlaag kunnen.

De clou zit 'm in het doorbreken van het dominerende grid-patroon van horizontale en verticale verbindingslijnen op huidige wafers, door ook diagonale verbindingen mogelijk te maken. Hierdoor zou het aantal benodigde connecties tussen transistors gereduceerd kunnen worden. Twee transistoren die diagonaal t.o.v. elkaar gepositioneerd zijn in de lay-out, kunnen dan door één metalen verbindingslijn gekoppeld worden i.p.v. met een horizontale en een verticale. De methode wordt daarom ook de 'X architecture' genoemd.

Naast het vervangen van aluminium- door koper-interconnects, is dit dus een volgende methode om elektrische signalen sneller door te kunnen geven in een chip. De methode wordt ondersteund door diverse chip-equipment fabrikanten, waaronder Applied Materials. Aandelen van Simplex stegen door dit bericht met 36,43% naar $38,20 (US). Simplex zal de software die gebruikt wordt voor het ontwerpen en virtueel testen van nieuwe chip-ontwerpen met de diagonale connects gaan verkopen. Toshiba zegt de nieuwe technologie toe te gaan passen in nieuwe chips in de tweede helft van 2002:

The method has the potential to obliterate the grid pattern that predominates microchip design by allowing circuits to be laid out diagonally, instead of only at right angles.

That could reduce the number of connections needed to link transistors, the microscopic switches that are crammed onto wafers of silicon and process the complex instructions of computers, cellular phones, and other electronics.

The new production method could improve chip performance by 10 percent, cut power dissipation by 20 percent, and increase production yields by 30 percent, Simplex said.

|