Introductie: E8500 met dubbele FSB

Het is ruim een jaar geleden dat Intel de 3GHz Xeon MP met 4MB L3-cache introduceerde. De chip voor servers met vier of meer processors had het qua performance al direct moeilijk tegenover zijn relatief nieuwe concurrent, de Opteron. Het gebrek aan 64-bit extenties, de beperkte bandbreedte en hoge kosten werden veelal aangewezen als zwakke punten van de Xeon MP. Intel compenseerde dat wel met extra RAS-features en een solide reputatie die zijn concurrent (nog) niet had, maar niettemin vroeg met name het technische publiek zich af hoe het bedrijf zou gaan antwoorden op de verwoede pogingen van AMD om het segment van 4-way servers 'open te breken'. Vandaag introduceert Intel dat antwoord in de vorm van Truland, een nieuw platform bestaande uit de E8500 Twin Castle-chipset en de nieuwe 90nm Xeon MP-cores Cranford en Potomac. In deze feature zullen we beschrijven op welke manieren Intel heeft geprobeerd om het gat met de concurrentie te dichten en welke mogelijkheden er in de toekomst nog benut kunnen worden om bij te blijven.

Het is ruim een jaar geleden dat Intel de 3GHz Xeon MP met 4MB L3-cache introduceerde. De chip voor servers met vier of meer processors had het qua performance al direct moeilijk tegenover zijn relatief nieuwe concurrent, de Opteron. Het gebrek aan 64-bit extenties, de beperkte bandbreedte en hoge kosten werden veelal aangewezen als zwakke punten van de Xeon MP. Intel compenseerde dat wel met extra RAS-features en een solide reputatie die zijn concurrent (nog) niet had, maar niettemin vroeg met name het technische publiek zich af hoe het bedrijf zou gaan antwoorden op de verwoede pogingen van AMD om het segment van 4-way servers 'open te breken'. Vandaag introduceert Intel dat antwoord in de vorm van Truland, een nieuw platform bestaande uit de E8500 Twin Castle-chipset en de nieuwe 90nm Xeon MP-cores Cranford en Potomac. In deze feature zullen we beschrijven op welke manieren Intel heeft geprobeerd om het gat met de concurrentie te dichten en welke mogelijkheden er in de toekomst nog benut kunnen worden om bij te blijven.

Een van de belangrijkste dingen die Intel aan moest pakken was de hoeveelheid beschikbare bandbreedte. Binnen het oude Xeon MP-platform is het namelijk zo dat tot vier processors een enkele 400MHz FSB moeten delen. Er is in die configuratie dus een schamele 800MB/s per processor aan bandbreedte beschikbaar, waarover niet alleen de communicatie met het geheugen, maar ook die met andere processors moet lopen. De eerste beslissing die Intel heeft genomen om daar verbetering in te brengen is om niet langer vier, maar slechts twee processors op een bus te plaatsen. Om toch nog vier processors per chipset te kunnen ondersteunen werd vervolgens een tweede FSB toegevoegd, waardoor de bandbreedte al direct verdubbeld werd. Bijkomend voordeel van deze beslissing was dat kortere bussen met minder belastingspunten ook hoger te klokken zijn, en dus kon men van 400 naar 667MHz gaan. In totaal is de bandbreedte hierdoor ruim verdrievoudigd naar 2,7GB/s per processor. Dit is nog steeds (veel) minder dan de Xeon DP en Opteron tot hun beschikking hebben, maar toch een grote stap in de goede richting, die een van de fundamentele bottlenecks van Intels serverplatform behoorlijk zou moeten verzachten.

|

| Bandbreedte per processor (GB/s) |  |

|

| Pentium 4 XE |    8,5 8,5 |  |

|

| Opteron 8xx |    6,4 6,4 |  |

|

| Opteron 2xx |    6,4 6,4 |  |

|

| Pentium 4 |    6,4 6,4 |  |

|

| Xeon DP (2006) |    6,4 6,4 |  |

|

| Xeon DP (2004) |    3,2 3,2 |  |

|

| Xeon MP (2005) |    2,7 2,7 |  |

|

| Xeon MP (2002) |    0,8 0,8 |  |

|

|

| Bandbreedte totaal |  |

|

| Opteron 8xx |    25,6 25,6 |  |

|

| Opteron 2xx |    12,8 12,8 |  |

|

| Xeon DP (2006) |    12,8 12,8 |  |

|

| Xeon MP (2005) |    10,7 10,7 |  |

|

| Pentium 4 XE |    8,5 8,5 |  |

|

| Xeon DP (2004) |    6,4 6,4 |  |

|

| Pentium 4 |    6,4 6,4 |  |

|

| Xeon MP (2002) |    3,2 3,2 |  |

|

Om de bandbreedte ook aan de andere kant van de pijp te kunnen vullen maakt de E8500-chipset gebruik van vier externe geheugencontrollers, de zogenaamde XMB (eXternal Memory Bridge) chips. Dit is een opvallende beslissing, want in plaats van het geheugen dichterbij de processor te brengen zoals AMD gedaan heeft, komt het bij E8500 dus juist een stap verder weg te zitten. Wat voor invloed deze architectuur heeft op de latency is niet bekendgemaakt, maar dat deze achteruit gaat is eigenlijk onvermijdelijk, zeker ook omdat er overgestapt wordt van DDR- naar DDR2-modules. De bandbreedte gaat er wel duidelijk op vooruit: iedere XMB ondersteunt dual-channel DDR2-400, en in totaal zijn er dus acht kanalen (oftewel 25,6GB/s) beschikbaar. Dit kan overigens niet volledig benut worden, want de zogeheten IMI-verbinding (Independent Memory Interface) die tussen de northbridge en de controllers zit ondersteunt maar 5,3GB/s. Hierdoor wordt het totaal beperkt tot 21,3GB/s, maar dat is nog steeds het dubbele van wat de FSB kan verwerken.

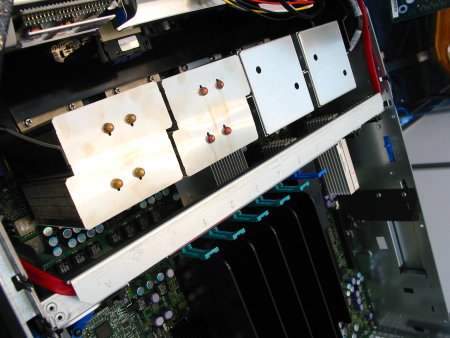

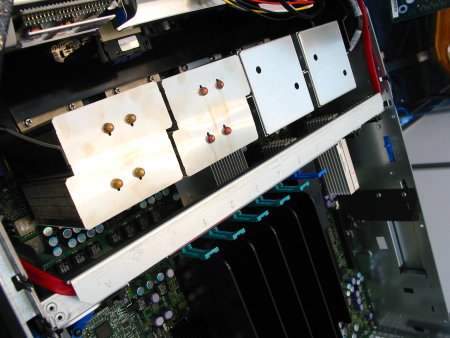

Extern geheugenbord voor Twin Castle-server

In het onderstaande diagram is te zien dat door de IMI-verbindingen dubbel zo snel gelezen als geschreven kan worden. Om het elektrisch ontwerp van het moederbord niet verder te compliceren en de ontwikkelkosten van de chipset te drukken is deze interface vermoedelijk gebaseerd op PCI Express. Deze standaard is unidirectioneel, wat betekent dat er voor communicatie van punt A naar punt B een andere lijn gebruikt wordt dan voor berichten in tegenovergestelde richting. Standaard PCI Express-slots zijn opgebouwd uit een aantal lanes (x1, x4, enzovoorts), waarbij iedere lane uit twee fysieke verbindingen bestaat. Als IMI werkelijk op PCI Express gebaseerd is dan zou het verschil in bandbreedte makkelijk te verklaren zijn door meer verbindingen upstream dan downstream. Wat voor gevolgen deze keuze heeft voor de prestaties is niet duidelijk, maar aangezien de meeste applicaties (veel) meer lezen dan schrijven en ook geheugenmodules over het algemeen minder snel kunnen schrijven dan lezen, zal het in veel gevallen waarschijnlijk niet eens te merken zijn.

Toegevoegde waarde in de chipset

Leuk om te weten is dat de E8500 feitelijk Intels eerste echte Xeon MP-chipset is. Het harde onderscheid tussen DP (2-way) en MP (4-way+) Xeons werd namelijk pas voor het eerst gemaakt met de komst van de Pentium 4-generatie, en sinds dat moment heeft Intel alleen nog maar chipsets voor de DP ontwikkeld. Het maken van MP-chipsets werd overgelaten aan bedrijven als IBM en ServerWorks. Intel wilde echter duidelijk laten zien dat ze de kunst nog niet verleerd zijn, en heeft Twin Castle volgestopt met de laatste features op het gebied van I/O en RAS, en voorbereid op toekomstige toevoegingen aan de processors. De northbridge heeft 28 PCI Express-lanes aan boord, goed voor drie x8-slots en één x4-slot. Ze kunnen echter ook gebruikt worden om bijvoorbeeld meerpoorts gigabit ethernet of PCI-X-bruggen op het moederbord te integreren. De southbridge is op zich niets bijzonders, maar de voor desktopgebruik enigzins verouderde ICH5 voldoet nog prima voor servers. Alleen het gemis van een (standaard) geïntegreerde SATA-controller zou een minpunt kunnen zijn ten opzichte van de nieuwere ICH6, hoewel het te betwijfelen valt of mensen die servers in deze klasse kopen daar wakker van liggen.

Intel Virtualisation Technology

Intel Virtualisation Technology

De chipset ondersteunt Intel Virtualisation Technology, beter bekend als Vanderpool. In het kort is dit een technologie die software om meerdere (instanties van) operating systemen tegelijk te draaien makkelijker en sneller maakt. Toepassingen als Virtual PC, VMware en Xen zullen op een processor met Vanderpool beter werken omdat enkele van de meest complexe en crashgevoelige handelingen die nodig zijn voor virtualisatie straks gevat zullen worden in enkele instructies. Hoewel daardoor op zich geen nieuwe mogelijkheden ontstaan, denkt Intel dat het door de komst van hardwarematige versnelling wel een stuk populairder zal worden. Ook toekomstige dual- en multi-coreprocessors zouden het percentage servers waar meerdere operating systemen op draaien kunnen verhogen, omdat nu eenmaal nooit alle software geschikt zal worden om te verdelen over meerdere cores. Verder ziet Intel toepassingen op het gebied van systeembeheer en beveiliging.

Active Management Technology

Active Management Technology

De oplettende lezer heeft in het bovenstaande diagram ook al AMT zien staan, oftewel Active Management Technology. Het idee voor deze feature is ontstaan op Intels eigen IT-afdeling, die moeite had om overzicht te houden over de vele tienduizenden desktops, notebooks en servers die het bedrijf wereldwijd heeft staan. Tijdens gesprekken met andere grote bedrijven bleek dat zij ook met dit soort problemen kampten, en dus werd besloten om aan een oplossing te gaan werken. Deze kwam in de vorm van een volledig autonoom deel van de machine; een simpele microprocessor, een simpel operating systeem en een klein stukje geheugen. Dit deel van het systeem werkt dus bijna volledig onafhankelijk van de rest. Of de machine nu gewoon in gebruik is, volledig gecrashed is of zelfs uit staat, de AMT kan van afstand benaderd worden om allerlei informatie uit te lezen. Naast de actuele status en hardwareconfiguratie van de machine kan bijvoorbeeld ook informatie over de fysieke lokatie en geïnstalleerde software in het AMT-geheugen worden gezet, zodat er altijd een overzicht is van bijvoorbeeld de hoeveelheid licenties die nodig is. Via AMT zou ook gecommuniceerd kunnen worden met een "Service OS", dat op de achtergrond patches installeert en ander onderhoud pleegt, terwijl de eigenaar van het systeem ondertussen gewoon doorwerkt op zijn normale OS.

I/OAT

I/OAT

I/OAT is een andere techniek die alvast verwerkt zit in de chipset maar nog wacht op omringende onderdelen. Met een combinatie van verbeteringen in software en hardware denkt men het verwerken van TCP/IP (en andere grote datastromen waaraan gerekend moet worden, zoals RAID) te kunnen versnellen. Volgens Intel zelf heeft dit in 90% van de gevallen een positief effect, maar daar werd niet bij verteld hoe groot dat effect was en wat er in de andere 10% van de gevallen gebeurde.

Reliability, Availability, Serviceability

Een belangrijke eis die vaak aan een server wordt gesteld is dat deze betrouwbaar is. Dat gaat veel verder dan alleen stabiliteit; het streven is vaak 99,999% uptime, dus ook tijdens onderhoud, de meest onwaarschijnlijke hardwareproblemen, pieken van kosmische straling of zelfs calamiteiten zoals een brand moet een server in principe gewoon foutloos door blijven draaien, of in ieder geval zo lang mogelijk. Met het nieuwe Xeon MP-platform is Intel erg ver gegaan om klanten te helpen dat streven te bereiken. Qua onderhoud kunnen processors, geheugenrepen en PCI Express-kaarten al toegevoegd en verwisseld worden zonder de stroom uit te schakelen. Vrijwel alle harde schijven voor servers ondersteunen ook al hot-swapping, dus bijna het hele systeem behalve het moederbord zelf kan uit elkaar gehaald en verbouwd worden terwijl het rustig door blijft draaien.

Daarnaast is het platform in staat om op allelei manieren defecte hardware te herkennen en isoleren. ECC - Error Correcting Code - is een bekende methode om eventuele fouten die tijdens het oversturen van data onstaan op te merken en te corrigeren. Het is bij servers vrij standaard om ECC op de geheugenbus te hebben, maar uniek voor Twin Castle is dat het ook op beide FSB's zit. Verder wordt het toegepast op de PCI Express-kanalen, zodat alle belangrijke communicatiepaden gedekt zijn tegen omvallende bitjes. Als het systeem opmerkt dat een bepaald onderdeel defect is zal het deze niet meer gebruiken, en in het geval van geheugen zelfs proberen te vervangen. De geheugencontrollers kunnen tot acht defecte chips opvangen voor ze falen, en zelfs in dat geval is nog niet alle hoop verloren. Zo kan er een online spare geïnstalleerd worden om een defecte reep automatisch te vervangen en kan desnoods het hele kanaal uitschakeld worden. Om dataverlies te voorkomen kunnen alle gegevens op twee plaatsen worden weggeschreven, en met Memory RAID ingeschakeld kan dat nog voor extra performance zorgen ook. De chipset wacht overigens niet af tot het misgaat, maar is in zijn 'vrije tijd' (waarin geen opdrachten van de processors verwerkt hoeven worden) continu bezig om te controleren of het systeem nog wel foutloos werkt. Hierdoor kunnen defecten al opgelost zijn voor de software ze ooit tegenkomt.

Value MP: prijsdruk op 4-way gebied

De nieuwe Xeon MP-processors Potomac en Cranford zijn gebaseerd op de laatste stepping van de 90nm Prescott-core. Dat wil zeggen dat ze alle nieuwste features aan boord hebben, zoals 64-bits extenties, EIST (Demand Based Switching) en het XD-bit. Hoewel de Xeon MP eigenlijk de eerste chip van Intel is waarvoor EM64T nodig was, komt de ondersteuning toch rijkelijk na die van de Xeon DP en zelfs iets later dan die van de normale Pentium 4. Dit is voornamelijk te wijten aan de veel strengere validatienormen die gelden voor Intels high-end serverchips, maar mogelijk is de timing ook zo uitgevallen vanwege de intentie om chipset en processor tegelijk te introduceren. Net als zijn voorganger maakt de nieuwe Xeon MP gebruik van een mPGA4 (Socket 604) verpakking. In 2006 zal in ieder geval de dual-core Xeon DP overstappen naar het nieuwe Socket J (LGA771), maar of dat ook voor de Xeon MP gaat gebeuren is op dit moment nog niet duidelijk. Intel belooft echter een lange levensduur voor dit platform, en het zou dus wel erg zuur zijn als een upgrade naar dual-coreprocessors niet mogelijk is.

Het voornaamste verschil tussen de Potomac en Cranford is het L3-cache van de eerste. Beide chips draaien op een 667MHz FSB met 1MB aan L2-cache, maar Potomac voegt daar 4 tot 8MB L3-cache aan toe. De prijslijst komt er als volgt uit te zien:

|

| | Klok | L3-cache | Prijs |  |

|

| Potomac |  | 3,33GHz |  | 8MB |  | $3,692 |  |

|

| Potomac |  | 3,00GHz |  | 8MB |  | $1,980 |  |

|

| Potomac |  | 2,80GHz |  | 4MB |  | $1,177 |  |

|

| Cranford |  | 3,66GHz |  | - |  | $963 |  |

|

| Cranford |  | 3,16GHz |  | - |  | $722 |  |

|

Hoewel er voor de zware Potomac nauwelijks iets verandert in het prijsmodel ten opzichte van de vorige generatie, ziet het "Value MP" segment er wel een stuk aantrekkelijker uit dan eerst. Niet alleen is de 3,16GHz Cranford de goedkoopste Xeon MP ooit, maar tevens is de kloksnelheid van de lager geprijsde versie voor het eerst even hoog tot hoger dan die van de dure uitvoeringen. Tot vandaag was het goedkoopste model een 2,0GHz-versie van $856, en werden klanten met een kleiner budget dus gedwongen om zowel cache als kloksnelheid in te leveren. Nu kan er echter voor het eerst een afweging gemaakt worden tussen cache en frequentie, zodat er vaker een gunstige prijs/prestatieverhouding uit komt rollen. Deels is deze verandering in het beleid te verklaren door het feit dat Intel voor Cranford standaard Prescott-cores kan gebruiken in plaats van afwijkende versies met L3-cache zoals voorheen het geval was. De concurrentie van de 700 tot 1500 dollar kostende Opteron 8xx-serie zal echter ook een reden zijn geweest om juist de goedkopere Xeon MP-versies aantrekkelijker te maken.

Het TDP van de nieuwe processors is gelijkgesteld aan dat van de Pentium 4 600-serie en de aankomende dual-core 800-serie: 130 watt. De E8500-northbridge gebruikt afhankelijk van het aantal actieve geheugencontrollers 17,9 tot 24,5 watt, en de geheugencontrollers zelf doen daar per stuk nog eens 8,5 tot 9,1 watt bovenop (waarbij DDR2 overigens zuiniger is dan DDR). Een volledig uitgebouwd 4-way systeem met de maximale geheugenconfiguratie verstookt dus alleen voor de genoemde onderdelen al meer dan 580 watt, ongeveer de helft meer dan een soortgelijk Opteron-systeem. Deze factor zal voornamelijk een rol spelen voor bedrijven die waarde hechten aan de fysieke dichtheid van hun serverpark.

Tegenstrijdige benchmarks

Hoewel we zelf helaas geen Xeon MP-server hebben gekregen om mee te spelen, hebben we inmiddels wel uit drie verschillende bronnen (IBM, Dell en Intel) informatie binnengekregen over de performance van het nieuwe platform. Deze bronnen kunnen uiteraard niet objectief worden genoemd, omdat ze de processors en servers die ze testen tegelijk ook proberen te verkopen, maar de resultaten kunnen wel een indicatie geven van wat er te verwachten valt.

Intel zelf claimt dat Truland 7 tot 65% winst ten opzichte van het vorige platform oplevert. Op het eerste gezicht ziet dat er goed uit, maar bij nadere inspectie blijkt dat de twee hoogste resultaten afkomstig zijn van synthetische tests, terwijl de twee laagste scores juist vallen in de meer realistische benchmarks, gebaseerd op het soort applicaties dat deze systemen in de praktijk zouden kunnen gaan draaien. Andere benchmarks van Intel (die we helaas niet mogen publiceren) tonen wel aan dat de snellere en verdubbelde FSB in combinatie met het grotere L3-cache de schaalbaarheid van het platform significant verbeteren, wat wil zeggen dat de performance van een 4-way systeem nu dichter bij het dubbele van een 2-way systeem ligt dan voorheen. Waarom deze verbetering niet goed terug te zien is in de 'echte' benchmarks is niet geheel duidelijk, maar kennelijk zitten de bottlenecks daar op andere plaatsen.

|

| Xeon MP Truland-platform (index 100 = vorige generatie) |  |

|

| SPECfp_rate_base2000 |    165 165 |  |

|

| Linpack |    157 157 |  |

|

| TPC-C SQL (64GB geheugen) |    130 130 |  |

|

| SPECint_rate_base2000 |    120 120 |  |

|

| TPC-C SQL (32GB geheugen) |    115 115 |  |

|

| SPECjbb2000 |    110 110 |  |

|

| SAP |    107 107 |  |

|

De eerste controversie in de benchmarks komt direct al met het tweede datapunt. In de aankondiging van de nieuwe Dell PowerEdge 6850 wordt namelijk een performancewinst van 32% gegeven voor SPECjbb2000 ten opzichte van de vorige generatie, terwijl Intel die zelf maar op 10% heeft geschaald. Welke van de twee dichter bij de waarheid zit is onbekend, maar het verschil tussen de resultaten van Intel en Dell is opvallend genoeg om nog wat extra zout op de rest van de benchmarks te scheppen.

|

| SPECjbb2000 (4-way servers, ops/s) |  |

|

| IBM Power5 1,9GHz |    170127 170127 |  |

|

| Xeon 3,6GHz - IBM |    167515 167515 |  |

|

| Xeon 3,3GHz/8MB - Dell |    155780 155780 |  |

|

| AMD Opteron 2,4GHz |    147301 147301 |  |

|

| Xeon 3,0GHz/4MB - Dell |    118031 118031 |  |

|

| Itanium 2 6M 1,5GHz |    116466 116466 |  |

|

Hoewel IBM het niet specifiek over het Truland-platform heeft gehad, brengt het wel een extra discussiepunt op tafel met zijn X3 'Hurricane'-chipset voor de nieuwe serie processors. Met deze chipset claimt het bedrijf een winst van 37% in TPC-C, net als Dell dus meer dan Intel zelf. Het opvallende is alleen dat IBM deze winst heeft gehaald met de goedkope Cranford-processors. Volgens het bedrijf is de X3-chipset zo efficient (ondere andere dankzij een bus snoop filter en sterk verlaagde geheugenlatency) dat de duurdere Potomac-chip met zijn grote L3-cache geen betere performance meer kan bieden. Benchmarks van Intel zelf - die we helaas ook niet mogen publiceren - beweren echter dat het L3-cache van de Potomac tot enkele tientallen procenten winst oplevert ten opzichte van de goedkopere Cranford. Het is onmogelijk om te weten of IBM het nut van L3-cache bagatelliseert, Intel het overdrijft, en/of de X3 echt zo ontzettend veel beter is dan de E8500, maar wederom werpen de benchmarks meer vragen op dan ze beantwoorden.

|

| TPC-C performance - quad processor servers (TpmC) |  |

|

| IBM eServer p5 570 |  | Power5 1,9GHz |  |    194391 194391 |  |

|

| HP Integrity rx4640 |  | Itanium 2 1,6GHz |  |    161217 161217 |  |

|

| IBM eServer xSeries 366 |  | Xeon MP 3,6GHz |  |    150704 150704 |  |

|

| HP Integrity rx5670 |  | Itanium 2 6M 1,5GHz |  |    136111 136111 |  |

|

| HP ProLiant DL585 |  | Opteron 852 2,6GHz |  |    130623 130623 |  |

|

| HP ProLiant DL585-G1 |  | Opteron 850 2,4GHz |  |    123027 123027 |  |

|

| IBM eServer xSeries 365 |  | Xeon MP 3,0GHz |  |    102667 102667 |  |

|

Conclusie - Update

Hoewel de benchmarks van verschillende bedrijven nogal wat tegenstrijdigheden vertonen, kunnen we er toch wel een conclusie aan verbinden. Intel heeft met Truland duidelijk een grote inhaalslag gemaakt. Echter, de voornaamste reden dat die slag zo groot is, is omdat de laatste nieuwe processor in de Xeon MP-serie een vol jaar geleden uitkwam en de oude FSB zelfs nog uit 2002 stamt. De E8500 heeft meer dan genoeg features en lijkt op dit moment ook weer krachtig genoeg om mee te doen met de concurrentie, maar de chipset moet nog wel een paar jaar meekunnen. De kans bestaat dan ook dat deze voor het einde van zijn levensduur weer achterop zal raken, waarbij het grootste potentiële struikelblok de dual-coreprocessors zijn. De drievoudige bandbreedte zal met deze chips meer een bittere noodzaak dan een luxe worden. Intel lijkt op het gebied van FSB echter nog wel speelruimte te hebben: de Xeon DP heeft bewezen dat een bus met twee processors naar 800MHz kan. Wellicht komt er een revisie van Truland uit op het moment dat de Xeon MP Paxville (90nm) of Tulsa (65nm) verschijnt.

De IBM X3-chipset met soortgelijke features als de E8500 (dubbele FSB op 667MHz, quad channel geheugen) lijkt het een stuk beter te doen door juist lagere in plaats van hogere latencies te bieden ten opzichte van de vorige generatie. En of het nou waar is of niet dat Potomac geen extra winst kan bieden op deze chipset, de resultaten die het bedrijf met de goedkope Cranford-processors neerzet zijn veelbelovend. Aan de ene kant zal Intel hier niet zo heel blij mee zijn, omdat ze liever de dure Potomacs en hun eigen chipsets verkopen. Aan de andere kant zien ze echter ook nog altijd liever een Cranford dan een Opteron over de toonbank gaan, dus wat dat betreft hebben ze niet te klagen over IBM's alternatieve chipset.

De volgende revisie van het Xeon MP-platform staat gepland voor 2007 en zal fundamenteel anders zijn dan alles wat Intel tot nu toe heeft gemaakt. De zogenaamde CSI (Common System Infrastructure) bestaat uit geïntegreerde FB-DIMM geheugencontrollers en op PCI Express gebaseerde interconnects om de FSB te vervangen. Om vier processors met elkaar samen te laten werken zal dan geen northbridge meer nodig zijn, en iedere processor die wordt toegevoegd zal ook extra bandbreedte met zich meebrengen, precies zoals nu al met Opterons het geval is. CSI zal zowel gebruikt worden door de Xeon MP Whitefield als door de Itanium Tukwila. De IA-64 en x86-64 architecturen zullen dan niet alleen worden verenigd qua chipset en socket, maar zelfs naast elkaar in hetzelfde systeem kunnen draaien.

Tot CSI verschijnt zal de E8500 in Intels chipsetassortiment aan kop staan. Bijgestaan door concurrent-partners als IBM moet de Xeon MP daarmee kunnen overleven, zeker nu Intel met de snelle Cranford-processors heeft toegegeven aan de prijsdruk van AMD. Of het genoeg is om de gestage opmars van de Opteron in 4-way serverland tot stilstand te brengen kunnen we alleen maar raden, maar het is in ieder geval te hopen dat beide bedrijven elkaar scherp zullen blijven houden.

Update (1-4-2005):

- Pagina 1: Correcte afkortingen voor IMI en XMB toegevoegd

- Pagina 1: Informatie over geheugencontrollers herzien (blijkt feitelijk 8-channel te zijn)

- Pagina 4: Stroomverbruik van Xeon MP en chipset toegevoegd

- Pagina 5: SPECjbb2000-resultaat IBM toegevoegd

- Pagina 5: Verbeterde score IBM in TPC-C doorgevoerd

- Pagina 6: Conclusie licht bijgeschaafd naar aanleiding van nieuwe informatie

Het is ruim een jaar geleden dat Intel de 3GHz Xeon MP met 4MB L3-cache introduceerde. De chip voor servers met vier of meer processors had het qua performance al direct moeilijk tegenover zijn relatief nieuwe concurrent, de Opteron. Het gebrek aan 64-bit extenties, de beperkte bandbreedte en hoge kosten werden veelal aangewezen als zwakke punten van de Xeon MP. Intel compenseerde dat wel met extra RAS-features en een solide reputatie die zijn concurrent (nog) niet had, maar niettemin vroeg met name het technische publiek zich af hoe het bedrijf zou gaan antwoorden op de verwoede pogingen van AMD om het segment van 4-way servers 'open te breken'. Vandaag introduceert Intel dat antwoord in de vorm van Truland, een nieuw platform bestaande uit de E8500 Twin Castle-chipset en de nieuwe 90nm Xeon MP-cores Cranford en Potomac. In deze feature zullen we beschrijven op welke manieren Intel heeft geprobeerd om het gat met de concurrentie te dichten en welke mogelijkheden er in de toekomst nog benut kunnen worden om bij te blijven.

Het is ruim een jaar geleden dat Intel de 3GHz Xeon MP met 4MB L3-cache introduceerde. De chip voor servers met vier of meer processors had het qua performance al direct moeilijk tegenover zijn relatief nieuwe concurrent, de Opteron. Het gebrek aan 64-bit extenties, de beperkte bandbreedte en hoge kosten werden veelal aangewezen als zwakke punten van de Xeon MP. Intel compenseerde dat wel met extra RAS-features en een solide reputatie die zijn concurrent (nog) niet had, maar niettemin vroeg met name het technische publiek zich af hoe het bedrijf zou gaan antwoorden op de verwoede pogingen van AMD om het segment van 4-way servers 'open te breken'. Vandaag introduceert Intel dat antwoord in de vorm van Truland, een nieuw platform bestaande uit de E8500 Twin Castle-chipset en de nieuwe 90nm Xeon MP-cores Cranford en Potomac. In deze feature zullen we beschrijven op welke manieren Intel heeft geprobeerd om het gat met de concurrentie te dichten en welke mogelijkheden er in de toekomst nog benut kunnen worden om bij te blijven.