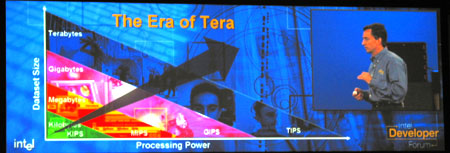

Op de derde en laatste dag van IDF hield Intels Chief Technical Officer Patrick Gelsinger een presentatie over "The Era of Tera", waarin hij een nieuw tijdperk in de geschiedenis van computers aankondigde. In de historie van de pc is het altijd al zo geweest dat de snelheid en capaciteit van de hardware gestaag toenam, maar dat mensen zich om de zoveel jaar begonnen af te vragen waarom ze nòg snellere chips, of nòg meer geheugen en schijfruimte nodig zouden hebben. De bekende uitspraak "640K should be enough for anyone" wordt aangehaald, maar er zijn ook veel recentere voorbeelden van zulke momenten te noemen. In 1999 schreef Information Week bijvoorbeeld nog dat 400MHz genoeg zou zijn voor iedere toepassing.

Het blijft natuurlijk altijd moeilijk om te voorzien welke processorintensieve applicaties er in de toekomst voor zullen gaan zorgen dat mensen en bedrijven willen upgraden, maar "the best way to predict the future, is to invent it", aldus Gelsinger, die hiermee een bekende uitspraak van pc-pionier Alan Kay aanhaalt. Kay was onder andere verantwoordelijk voor de eerste Windows-achtige GUI en stond aan de wieg van object oriented programmeertalen. Volgens Intel kan de hele wereld beschouwd worden als data: ieder aspect van ons leven kan wel op een of andere manier in bytes worden uitgedrukt. Het probleem is alleen dat data verzamelen of vastleggen op zich nutteloos is zolang je er niets of weinig mee kunt doen, en Intel ziet de toekomst dus in RMS-applicaties: Recognition, Mining en Synthesis.

Recognition betekent letterlijk "herkenning", en daarbij kun je dus denken aan het herkennen van spraak voor de beveiliging of besturing van de computer, maar ook aan het zoeken naar verdachte figuren op (live) videobeelden of het vinden van afwijkingen in röntgenfoto's. Mining is het gebruiken van data uit verschillende bronnen, zoals een database met criminelen combineren met videoherkenning, statistieken uit iemands complete medische geschiedenis kunnen halen om betere diagnoses te kunnen stellen of het automatisch verzamelen van informatie over een onderwerp op internet. Synthesis staat voor het uitvoeren of weergeven van data op verschillende manieren. Fotorealistische beelden, animaties, natuurlijk klinkende spraak en automatisch gegeneerde documenten. Hoewel dit natuurlijk vrijwel allemaal dingen zijn waar vooral een berg slimme software voor nodig is, moeten toekomstige generaties hardware met dit soort applicaties in het achterhoofd worden ontworpen om het echt soepel te laten lopen.

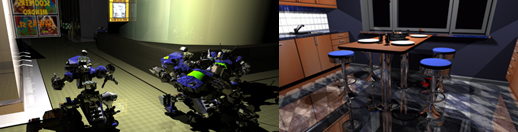

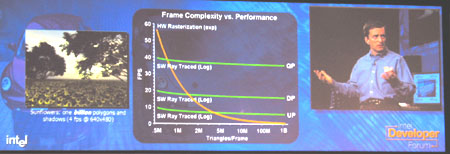

Een voorbeeld dat wordt gegeven is graphics. De laatste jaren zijn videokaarten met sprongen vooruit gegaan, maar nog steeds is duidelijk zichtbaar dat realtime gerenderde beelden nep zijn. Dr. Philip Slusallek van inTrace legt uit dat dit een fundamenteel probleem is van de huidige aanpak. Een videokaart verwerkt één triangle per keer en er worden allerlei trucs gebruikt om te zorgen voor effecten als schaduw. Dit is misschien wel acceptabel voor spellen, maar een bekende autofabrikant baalde toch flink toen bleek dat het dashboard van het prototype bleek te reflecteren op de voorruit, iets wat de "tricks" van standaard rendermethodes niet hadden laten zien. inTrace ziet de toekomst liggen in raytracing, een techniek waarbij de fotons die door de scene vliegen gevolgd worden waardoor een extreem nauwkeurig en realistisch plaatje ontstaat inclusief natuurkundig verantwoorde schaduwen, spiegelingen en (indirecte) belichting.

Het nadeel van raytracen is dat het extreem langzaam is op de huidige hardware. Het bedrijf van Slusallek is volledig toegewijd aan het optimaliseren van de algoritmes, maar heeft nog steeds een cluster van 23 dual 2,2GHz Xeon-servers (400 gigaflops) nodig om een VW New Beetle een beperkte resolutie te kunnen renderen met een framerate die wij tussen de 10 en 20 schatten. Het voordeel is daarentegen dat de raytracer extreem goed schaalt. Ten eerste maakt het nauwelijks uit of er nou 1 miljoen of 1 miljard polygonen zichtbaar zijn in een bepaalde scene, terwijl een traditionele GPU eigenlijk alleen maar goed presteert als het aantal polygonen klein genoeg gehouden wordt. Ten tweede kan de raytracer iedere extra processor die wordt ingezet bijna voor de volle 100% benutten, waardoor de techniek zeker op het moment dat Intel meerdere cores per processor gaat leveren steeds aantrekkelijker wordt.

Het leveren van extra performance voor dit soort applicaties wordt een steeds grotere uitdaging. Kloksnelheid verhogen wordt een steeds groter probleem. Ten eerste vanwege het stroomverbruik, iets wat wel blijkt uit de TDP-waardes van Prescott (103 Watt) en Tejas (115 Watt). Ten tweede vanwege de immer groter wordende latency richting het geheugen: een 486 had nog maar 10 cycles nodig om iets uit het geheugen te halen, maar op een modern Pentium 4-systeem is dat al 220 cycles. Ook de snelheid waarop signalen zich verplaatsen binnen de chip is een beperkende factor geworden. Op 65nm duurt het al 15 cycles puur om iets van de ene naar de andere kant van de chip te krijgen. De meeste methodes om deze effecten te verbergen of compenseren zijn al afgekeken van mainframes, maar de ideeën uit die hoek zijn nu zo ongeveer op. Nu gaat men dus een hele andere kant op kijken; de HPC (high-performance computing) markt, parallellisme dus. HyperThreading was slechts een kleine stap in die richting, in de toekomst gaat alles "multi" worden: cores, geheugens, bussen, caches, noem maar op.

Er is een prototype compiler ontwikkeld om plaatsen in de code waar geheugenlatency een probleem wordt te herkennen en op die plaatsen helper threads aan te maken die data alvast beginnen te cachen. Er is weinig extra complexiteit in de hardware nodig, maar een demonstratie van IBM DB2 op een sample van een toekomstige Itanium laat een performancewinst van 10% zien. Het aantal keren dat er voor het doorzoeken van de enorme database naar het geheugen gegrepen moest worden omdat iets niet in het cache stond was bijna gehalveerd van 411 naar 214 miljoen keer dankzij de helper threads, en er is nog ruimte voor verbetering aangezien de techniek zich nog in het beta-stadium bevindt.

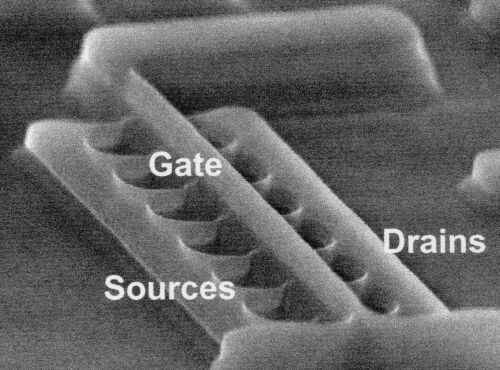

De architectuur zal zich op meerdere manieren moeten kunnen aanpassen aan het soort applicatie dat erop gedraaid wordt. Op chip-niveau kan dat gerealiseerd worden met behulp van Adaptive Body Biasing. Door extra stroom op een transistor te zetten kan hij (tijdelijk) even snel schakelen als een transistor van de volgende generatie ten koste van meer hitte. Andersom is echter ook mogelijk: lekstromen - tegenwoordig verantwoordelijk voor 30 tot 40% van het totale opgenomen vermogen - kunnen met Reverse Body Biasing (tijdelijk) tegengehouden worden ten koste van performance. Ook heeft men chips waarvan de elementen op meerdere manieren met elkaar verbonden kunnen worden om verschillende functionaliteiten te realiseren. Zo heeft men een gecombineerde 802.11b/a/g en GPRS-chip gemaakt die twee keer kleiner en zuiniger is dan de concurrentie, en ook hier ging het nog om een vroege, niet geoptimaliseerde, versie.

Ook op hoger niveau valt er nog genoeg te optimaliseren, zodat er een maximaal aantal CPU-cycles beschikbaar is voor applicaties van de gebruiker. Iets als het verwerken van TCP/IP-pakketten is bijvoorbeeld een noodzakelijk kwaad, eigenlijk zou zoiets gewoon moeten werken zonder dat het processortijd opeet. Er zijn wel hardwarematige TCP/IP-engines beschikbaar, maar die pakken de echte problemen niet aan, want van de 2100 cycles die een gemiddeld pakket in beslag neemt is maar 22% daadwerkelijk TCP/IP-verwerking. 23% van de cycles gaat verloren aan geheugentoegang en maar liefst 58% is overhead van het OS. Samen met de eerder beschreven helper threads kan Direct Cache Access (een afgeleide van Direct Memory Access - DMA) en een geoptimaliseerde stack de performance met wel tien keer verhogen.

Omdat dit soort dingen natuurlijk wel per toepassing verschilt zal het belangrijk worden om hardware en software op elkaar te laten inspelen. Niet alleen moet de software een bepaalde architectuur kunnen herkennen om optimaal gebruik te maken van de mogelijkheden, maar het moet ook mogelijk worden voor software om zijn wensen op het gebied van performance naar de hardware te sturen, zodat zaken als processorcores, caches en bussen dynamisch geconfigureerd kunnen worden.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()